DDR3布线的那些事儿(三)【转发】

2017-10-13 by:CAE仿真在线 来源:互联网

问答DDR3设计中那些因素会影响时序,在设计中该怎样避免呢?上次问到影响DDR时序的因素,其实DDR是一个牵一发而动全身的整体,所以对于它的时序,影响的因素太大,比较突出的是—>电源完整性,走线拓扑和端接,等长,串扰<—这四个总体的因素。电源完整性,对于时序是一个影响比较大的因素,电源不稳定的话,会给信号带来很多影响,上升沿,下降沿,抖动等等,所以电源方面的处理是需要重点关注。VDD电源的话,主要是关注滤波电容的容值、布局,以及储能电容的分配和电源地平面之间的耦合,最好用完整的电源平面处理;VTT电源需要对应有滤波电容,以及比较宽的载流通道;vref电源则主要考虑其稳定性,保证滤波电容靠近PIN脚放置。

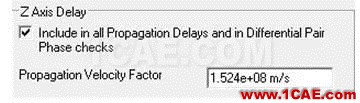

走线拓扑和端接包含的细节比较多。1、通过判断主控芯片是否有read write leveling功能,来判断选用T拓扑还是Fly-by拓扑。2、走线同组同层,因为微带线和带状线的信号传输速率不一样,微带线速率更快一些。3、阻抗匹配,阻抗失配的话,会引起比较大振铃,对于时序也有一定的影响,布线的时候要注意线宽一致,不跨分割。4、容性负载补偿;尤其是选用fly-by时,负载颗粒越多,拓扑分支走线阻抗就会越低,可以选择适当加粗第一个颗粒到芯片的走线或者或者减小分支线宽这钟简单的方法。5、考虑过孔长度对时序的影响,也就是我们常说的Z轴延时,在软件中打开下图所示的功能,并且将层叠在软件中设置好。

等长是最直观的时序匹配手段,是最重要的影响因素,需要注意的细节有以下几点:

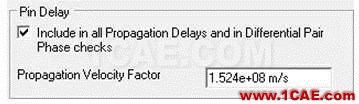

以上基本就是问题的答案,下面是大家的回答:(以下内容选自网友答题)影响时序的因素有:走线等长,走线阻抗,走线拓扑结构,驱动Buffer和匹配的Odt,IO电源和Ref电源性能,参考面的层叠结构,软件配置等。 如何减小这些因素的影响呢:第一,对于走线,严格控制DQ与DQS的Skew,不同控制芯片有差异,时钟等重要信号保障好(满足至少3W);第二,对于阻抗、拓扑、驱动和Odt的最佳配置,需要仿真给出最优的信号质量下的参数;第三,对于电源,需要保障噪声满足要求的前提下,越小越好;第四,层叠结构,走线走线参考GND,其次只能参考自身的IO电源;第五,软件配置,确认芯片是否支持Writeleving,确保仿真推荐配置落实等。@杨勇评分:3分1,vref电源不稳定会影响时序; 2,同组走线不同层走,如同组的dqs和dq分开走内外层; 3,走线长度计算没有考虑芯片内部的走线长度,导致走线时间延时不一样; 4,信号走线阻抗匹配不好,会引起信号回冲,振铃,毛刺等采样异常,引起时序不满; 5,ddr控制器不支持读写平衡,而采用fly by的走线方式;@hk评分:3分1.走线的相对长度:做等长处理; 2.蛇形线串扰:增大蛇形线间距,减小蛇形高度; 3.信号建立时间/保持时间:调整驱动能力,减小寄生参数; 4.信号边沿陡峭度:通过合理布局布线减小寄生参数;@二羔子评分:3分1、从CPU和DDR3的角度来看,需要给CPU和DDR3芯片提供“干净”的电源、参考电压VREF以及上拉VTT电压,从源头上降低并行信号的时序抖动:电源平面和地平面越小越好;滤波电容与芯片引脚越近越好。 2、从信号传播路径上看,需要优化PCB走线设计:同组信号走在同一层,参考地平面最好;信号不跨分割;阻抗控制,减小反射;保证足够信号间距,减小串扰;导入IBIS模型进行PCB前仿来优化走线等长,不要一味追求数值上的绝对等长@ 海鸥评分:3分首先,布线长度和等长会影响时序,相对严格做好等长,比如分段、分层等长。其次,外界的干扰和组内的干扰也会影响时序。相对拉大布线空间,远离干扰源(如高速信号、晶振、连接器IO口等等)。数据线同组同层尽量严格等长。地址线允许的误差大,可以走在不同层。@ 龍鳳呈祥评分:3分走线长度、串扰、会影响时序,设计时注意设置好等长规则,走线长度控制在误差范围之内,考虑信号与电源之间的干扰,保证电源的干净和信号的质量。必要时加上pin delay 和过孔长度。@ 清晨的阳光评分:3分1.优化主电源和vtt上拉电源:电源芯片与ddr3模块尽量近,电源平面与地平面尽量近,合理放置虑波电容,vtt上拉走线尽量短。稳定的电源对信号的上升、下降、占空比、抖动时间很重要。 2.优化vref:合理将滤波电容放置在芯片引脚端,越近越好。稳定的参考电压,对眼图模板的电压位置很重要。 3.优化串扰:同组信号走在同一层,不跨分割,加大间距。串扰越小,源同步并行信号的skew越小,利于增加建立保持时间裕量,高温,高湿等特殊环境下的稳定性更强 4.阻抗控制,调整odt优化信号质量@Ben评分:3分过孔、跨分割、不同层走线、分支桩线都会影响时序。应尽量少打过空,走线尽量不跨参考,同一数据组走线走同层,尽量减小分支桩线的长度。@涌评分:3分影响因素芯片时钟锁相环的抖动,I/OBUFFER时钟树的偏斜,封装、PCB布线偏斜,同步开关噪声、串扰、码间干扰等信号完整性问题以及接收端芯片的固有延时,包括接收芯片的建立、保持时间,信号边沿Slew Rate变化导致的建立、 保持时间需求的增加。 为满足DDR3时序,地址线和每组数据线都要进行等长处理,以达到时序要求。数据线组内长度误差控制在±5mil以内;地址线长度误差控制在±25mil以内。若有空间绕等长的话可以把误差再控严格点。等长时,数据线以DQS线为基准线进行等长处理,地址线以时钟线为基准线进行等长处理。@Lee评分:3分1、信号布线长度,在满足等长空间,间距的及其他要求情况之下应该尽量短;2、器件引脚PIN Delay,在做等长的时候赢吧这个考虑进去;3、同组信号扇出走线长度不一样,应保证同组信号在表层扇出的长度误差尽量小;4、同组信号部分跨分割,应保证同组信号都不夸分割。5、同组信号走线之间间距差异大,间距太小的串扰大,应保证所有信号线之间间距满足3H,或者更大。@ Jamie评分:3分1,层面:不同层传输速度不一致,且还有z轴长度影响,因此同组信号同层走线2,长度:在pcb上严格控制各组信号等长,有pin delay的芯片要考虑进去 3阻抗:严格控制阻抗,芯片较多时注意容性负载补偿@业叶夜耶评分:3分1、叠层过孔等Z轴的影响,密切与板厂合作,了解“PCB的筋骨皮”和“高温高压终成一家:线路板的层压”,精确叠层结构。使用背钻、反焊盘等方法优化过孔设计。2、串扰的影响,分为同层线间串扰,和不同层串扰。设计时加大线间距,不同层垂直布线且加大层间介质厚度。3、同步开关噪声能给信号带来100ps左右影响。设计时重点是减小回路电感:良好的滤波电容布局布线,优化电源地和信号回流路径,准确的Vref,足够线宽的VVT电源线。4、Derating补偿的影响,按芯片手册正确提取数值在软件中设置。5、码间干扰ISI,不能解决,设计时优化串扰等其它方面的影响,空出余量来抵消ISI的影响,期待DDR4的DBI功能。@山水江南评分:3分1.确保ddr的电源稳定性,包括vdd.vtt.vref,注意滤波电容的分配,这样才能保证信号质量。 2.信号线的串扰,保证时钟.数据.地址各自以及相互间的间距,并且数据位的同组同层,不跨电地分割,减少串扰能利于增加建立保持时间裕量 3.信号阻抗控制,布线时减少阻抗不连续,减小过孔分支,减少终端上拉电阻的布线长度。4.线长控制,以及各组的等长控制,主要是数据和dqs之前的等长,地址间等长@ 刘栋评分:3分首先是器件,支不支持flyby,影响DQS和clk时序控制,然后是等长走线(包括换层,z轴延迟,蛇线类型和过孔这些,文章讲得很多了),还有就是pcb加工误差,除此之外的信号线串扰,电源开关噪声,端接电阻都会影响时序。@ 大海象评分:3分电压值是Vdd的一半,容差为+/-3%。 Vref不稳会造成时序抖动、错误,以及高低电平的误判即误码等。@轩评分:1分第一,数据组内等长,误差控制在20MIL以内; 第二,地址、控制信号以时钟作参考,误差控制在100MIL以内,需要严格控制CLK与Address/Command、Control之间的时序关系,确保DDR颗粒能够获得足够的建立和保持时间。 第三,同组信号走在同层,保证不会因换层影响实际的等时;同样的换层结构,换层前后的等长要匹配,即时等长; 第四,考虑VIA对走线长度的影响; 第五,注意绕线方式对串绕的影响,也会影响信号延迟@ 王发展评分:3分从根本上来讲,高速串行传输的时序问题,归根结底是信号质量的问题。1.电源是一个重头戏,芯片的电源、晶振的电源处理,滤波电容等等都非常关键。2.布线方面,参考平面的选择,层叠结构的安排走线层的排布,差分对的设计等都不容忽略。上一篇介绍中的布线原则,走线,阻抗,拓扑,等长处理等都与之相关。3.其它如模态转换,反射,串扰等都是潜在因素!@杆评分:3分1.等长:信号线分组,同组同层,等长 2.串扰:同组线间距3w,非同组5w,有完整的参考平面 3.阻抗是否连续:单线50ohm,差分100ohm,完整的参考平面,回路面积最小 4.电源完整性处理。@王萍评分:3分1.各组信号线内没有严格控制等长 2.vref电压不稳定会影响建立时间和保持时间 3.组内各信号走在不同层,由于微带线和带状线对信号的传输速度不一样会影响时序 4.信号之间的串绕严重时会导致信号上升沿,下降沿时间发生变化,也会导致DDR时序发生偏@Jasen评分:3分影响DDR时序的关键是信号的质量问题,主要因素有:信号接收端的建立时间和保持时间有足够裕量;减少信号的抖动问题;降低信号间的串扰等。 具体在DDR设计时,要注意的问题比较多,比如:满足信号阻抗要求;同组数据线与选通信号做到同层等长走线;地址\命令\控制信号与时钟信号要满足长度关系;处理好DDR的各类电源(VDD、VTT、VREF),比如滤波电容的分配、电源平面靠近地平面等;各组信号间距处理好;注意蛇形线的绕线方式等等。@ly评分:3分内外层走线延迟不同,同组同层走线处理;不过地址和控制线线可能会走不同层,要把切换孔的长度加进去,因此就要注意在绕线之前把叠层设计好,填入叠层中,系统自动填加长度和计算延迟进去;@GFY评分:2分DQS线不同平台所要求的阻抗是不一样的,不能千遍一律是100OHM,误导人。@徐增评分:2分所有的时序计算都是以恒定的时钟信号为基准,实际中会有抖动和偏移问题,产生的原因和晶振或者PLL内部电路有关。板级传输中信号完整性对时序的影响很大,比如串扰会影响微带线传播延迟;反射会造成数据信号的波动。时钟走线的干扰会造成时钟偏移。对于设计中的源同步总线,保证线长的匹配就行了。@Melo评分:2分

1、2、3、4、6、7、8、10、11、12、13、14、16、17、18、19、20、21的回答很详细,均给3分。

5,、9、15对于设计中怎么处理,答案没有列举到3点以上,所以给2分。

大家回答中的关于调试中的ODT和buffer的选择,由于这次的问题是在设计中怎么避免,所以不算在答案中。

原作者及出处——一博科技“高速先生”

开放分享:优质有限元技术文章,助你自学成才

相关标签搜索:DDR3布线的那些事儿(三)【转发】 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析

编辑