老司机和您谈一谈串行总线怎么比并行总线快?

2017-04-03 by:CAE仿真在线 来源:互联网

编者按:当前,在高速硬件电路设计中,主要就分为两类信号类型,一类是串行信号,一类是并行信号。两类信号的特点不一样,其分析的手段也都不一样。

作为一个电路设计师,我整个职业生涯都花在接口电路上,串行并行都做过,且速度不慢(DDR3-1600Mbps, SerDes 30Gbps),这个问题不答实在技痒难耐。已经看到的答案中,大家基本上都命中了关键的知识点,但是没有把背后的逻辑说清楚,也没有人从电学特性和经济 的角度分析这个问题。大言不惭,欢迎大家拍砖。

----------补充--------

名词解释:

Mbps, Gbps: 一百万比特每秒,十亿比特每秒

skew:时间偏差,A比B快/慢一秒,就叫skew一秒

PCB:印刷电路板,也就是大多数电路板

IO: 输入输出电路

cable: 线缆

SerDes:串行转并行,并行转串行

还有人说串口最快的,我们来算一算。业界目前大量应用的28Gbps SerDes,传一个比特只要35.7皮秒,这点时间光在真空中可以走上一厘米,连角膜到视网膜都不够。哪个快?

----------正式答案的分割线--------

先说我的答案,串行接口为啥比并行接口快?是因为串口的特性和应用场景,决定了它更加适合采用一些提高单根信道速率的设计方法,这些方法用在并口上并不合适。

讨论这个问题,首先要搞清楚定义,什么叫并行接口(parallel link)? 什么叫串行接口(serial link)?这就可以吵一天。

并口代表DDR说:“我是并口的纯正血统杰出代表,每8bit要附带一对DQS线作为时钟,每个bit都要同步到这对DQS上去,skew超标就不能工 作,64位DDR3-1600总带宽可以到100Gbps,哪个串口做得到”?鄙人冷笑,说:“别以为我不知道你的底细,别看你IO是1.6G,内存控制 器给你的一般都是4位并行的400M,你要先悄悄做一下并行转串行,再输出。何况你传64bit数据需要80根全速率的DQ/DQS线,还要20多根半速 率命令地址线,平均下来一根线1G还不到”。

XAUI举手问:“我算串口么?XAUI一定是8组16根差分线,4组读4组写,缺任何一组都不符合协议,看着很并行啊?” 32位的PCI-E也一脸关心的等着答案。

我们先这么定义:在一个独立的信道上,每次同时传输1bit为串口,每次同时传输多个bit为并口。 标准的串口如XAUI,HDMI等,每对差分线组成一个信道(channel),每个信道是否能成功传输并不取决于其他信道。而DDR这种,10根线组成 一个信道,每次同时传8bit,错了某一bit只能重新传,便是标准并口,芯片内部的并转串和IO并不相关,不影响定性。按照这个定义,大家看看各种接口 协议怎么划分呢?我觉得已经很清楚了,以单个channel的传输速率衡量,串口一般来说更快。下一个问题就是,为什么呢?

这是一个电学问题,但首先是一个经济问题。

对任何一种协议,提高总带宽不过是两种办法,首先要提高单根线的传输速率,其次只能增加电线的数目。增加线的数目实在费钱,首先现在的芯片往往IO都很紧 张,增加了IO PAD还要搭上额外的ESD和面积;封装和PCB上增加额外的线更复杂更贵这就不用说了,对于某些用cable的协议基本就是不可接受的。你是愿意插16 根网线还是一根?接电视机的时候喜欢一根线的HDMI,还是五根线的RGB+音频?还有 @Arthur Wang 提到的150米长线。。。。。。何况并口还要对这些线进行长度匹配,想想头就大了。

历史上,工程师们确实是先做了串口,速度不够没办法只好含泪加电线上并口,直到他们发现了三大法宝来提速,并口的动力就不那么强劲了,正如 @auxten 所言。但是在芯片内部,增加总线宽度的代价并不高,因此CPU里面有个1024位的数据总线也不奇怪。

为了提高单根线的传输速率,必须要讲到我们模拟电路工程师的三大法宝,差分信号(differential signaling),时钟-数据恢复(Clock-Data Recovery,简称CDR),和信道均一化(Channel Equalization,Eq)。

差分信号的好处 ,不外乎抗干扰能力强,引入的噪声也比较小,虽然必须要两根线,但速度从几百M提高到几G,还是很值得的。

CDR的好处 @龚黎明 也说过了,消灭了skew,减少了时钟的功耗和噪声(但多出了CDR电路本身的功耗和噪声),同时避免了电磁干扰。想想在PCB或者电线上传一个15G的时钟,太带感了,幸亏我们不用做这种事。

信道均一化 相当值得一提,这才是SerDes高速发展的决定性因素,所以我决定花点文字讲一下。

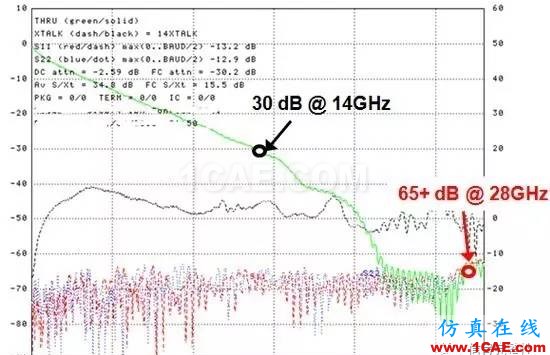

一般来说,真实世界中的信道都是低通特性的,到处都是小电容,所谓绝缘体中的分子在高频情况下吸收电场能量,再加上金属线中的趋肤效应,所以我们想要的高频信号走不了多远就不像样子了,比如下面某信道的频率特性(绿线)。

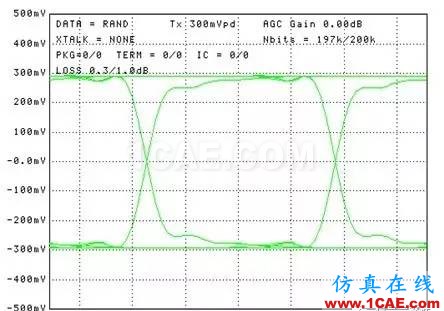

如图所示,在对应28Gbps的频点上,信号能量被衰减了30db,电压幅度只剩3%了;在对应56Gbps的频点上更惨,65db意味着信号电压摆幅剩下不到千分之一。在这种信道中,发送端一个完美漂亮的数据眼图:

到了接收端会变成这样的一堆杂乱的信号波形:

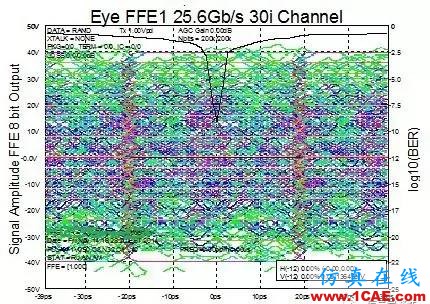

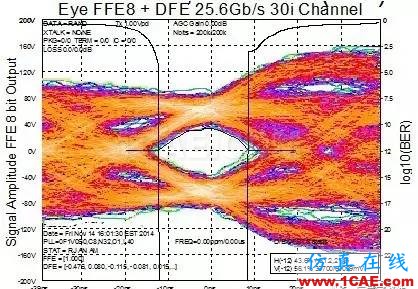

什么都辨认不出来对吧。但是,经过我们聪明的工程师们一番努力,均一化开关打开,信号就变成了这样:

神奇么?我觉得挺神奇的,我认识的电子工程师们第一次看到这个,没人觉得不神奇。

下面一个重要的问题,既然有了三大法宝,他们只能用在串口上吗?

答案很显然,不是,串口可以用的,我们并口一样可以用。那为什么并口不用呢?

差分信号这条不用说了,并口的电线本来已经够多了,数目还要再翻一倍?系统工程师会杀人的。

CDR 意义也不大,反正你并口速度也不高,一堆数据线中顺便传下时钟,比做接收端做CDR再采样每一位数据省事多了。

信道均一化属于屠龙之技,不用差分信号的话也就传几百M,本来就没啥衰减,用这个干啥?还是考虑下各种噪声串扰的问题吧。

于是答案就呼之欲出了。串口为啥比并口快?是因为串口的特性和应用场景,决定了它更加适合采用一些可以提高单根信道速率的设计方法,这些方法用在并口上并不合适。

从现有的应用看来,需要持续稳定高带宽的应用,往往使用高速串行接口,一根带宽不够再加一根,各种视频网络应用,基本如此。而一些历史遗留速度不高的应用, 还有一些需要突发性高带宽的应用,并口仍然存活,比如很特殊的DDR。虽然XDR/GDDR/HMC/HCM这些新标准都在试图引入SerDes, 但DRAM行业的特殊性还是让并口继续存活着。

相关标签搜索:老司机和您谈一谈串行总线怎么比并行总线快? HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析