利用仿真技术优化电路板设计

2016-11-01 by:CAE仿真在线 来源:互联网

为支持物联网和大数据要求的海量数据传输,需要使用100千兆位以太网等高速网络技术。这给设备供应商带来了巨大的挑战。板上高速通信通道目前正朝着25-28Gb/s和更高速度发展,几乎是一年前先进水平的两倍。随着数据速率增大,位周期(为发送每一位分配的时间)已经缩小到不足40皮秒。这显著低于位从发射器传输到接收器所用的时间。印刷电路板(PCB)材料引起的插入损耗随频率增大,造成通道上因物理损耗和反射导致的眼图闭合(减弱的信号)概率增大。在这样的条件下实现可靠的链路极具挑战性,即便在不考虑成本和上市速度的情况下也是如此。但是在今天成本竞争激烈的环境中,制造商无法承担使用独特高端材料和组件的成本,除了在绝对必要的情况下。

ANSYS 为新一代无线集成推出配备3D EM 组件库的全新电子桌面

高速互联设计挑战

传统方法通常让设计人员对一些问题心存疑虑:设计是否能在所有可能的条件下保持功能和鲁棒性、是否选择了成本更昂贵的电路板材料、是否需要使用带状传输线或微带传输线来满足设计规范等。依靠构建物理测试原型来评估仅仅一种设计方法时,就要耗费超过10万美元的成本和数月时间开发。在如此之高的信号传输速率下,基本上无法进行任何水平的设计、验证与测试(DVT)。在电路板上开展测量的区域会导致眼图闭合,因为测试不能在传输线末端进行,需要深入封装和器件内部。如果设计人员只能猜测重新设计所需的变更,那么整个高成本的周期会重新开始,并很有可能需要重复。由于无法在时间和成本约束下开发出鲁棒性设计,数家小型网络设备创业公司已关门歇业。

被抽取通道的ANSYS HFSS S21 插入损耗图

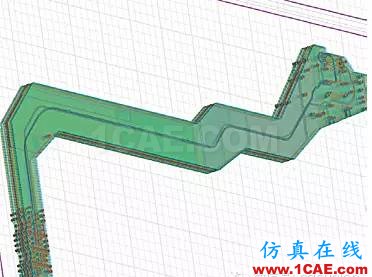

28 个6 英寸Gb 通道之一的开口截面ANSYS HFSS3D 布局

仿真技术与这种猜测和经验法则方法有着鲜明相比,它把信心和科学带入工程过程。在设计阶段早期或甚至在开发周期后期,通过时域和频域仿真的结合,能够让工程师最深刻地了解某个接口或通道是否是可靠的。例如,可能时域仿真给出的眼图说明该通道工作正常,但频域提示有意料之外的缺口。通过仿真检查构成系统通道的每一个电路元件,有可能发现设计的哪一个方面(通孔、太靠近接地面的差分对、组件布局问题或材料问题)出现了问题。

100千兆位以太网网络产品

Interconnect Engineering是一家服务于创业企业到财富500强企业的独立咨询公司。Interconnect Engineering的客户之一是一家生产多种100千兆位以太网网络产品的网络设备供应商。某特定设计在一个球栅阵列(BGA)和一个四通道小型可插拔(QSFP)光学模块之间双向运行四个通道结合的28Gb/s链路。由于该客户设计所支持的物理布局难以满足供应商提出的指南和约束要求,设计涉及的风险在增大。为避免公司反复进行一系列电路板设计,造成数十万美元的成本和数月的开发时间,该供应商要求Interconnect Engineering在构建原型之前仿真该设计。

虽然Interconnect Engineering公司一直使用和支持ANSYS电子设计工具,但此项目让该公司有机会使用到全新推出的ANSYS Electronics Desktop。该工具在这个应用上体现的重大优势是它能够节省在时域和频域中分析设计所需要的时间。Electronics Desktop集成了EM工具、电路/系统仿真、ECAD链路和合规性报告功能。这种新技术为ANSYS HFSS、HFSS 3D Layout、HFSS-IE、Q3D Extractor和HFSS Planar EM电路和系统仿真等设计类型提供了统一桌面。用户能够利用电磁仿真和电路仿真之间拖放式动态链接,将HF/SI分析插入到并存的项目中,从而简化问题设置和提供可靠性能。在统一的图形化用户界面中工作,而无需在多个不同的程序间来回切换,可以避免从一个程序向另一个程序导出数据。例如用户使用简单的导入功能就能够把S参数单元或IBIS-AMI模型插入到电路仿真中。总而言之,Electronics Desktop为求解复杂问题提供了明显的效率改善和易用性。

ANSYS Electronics Desktop 集成了EM工具、电路/ 系统仿真、ECAD 链路和合规性报告功能。

电路仿真器中所示的28Gb 接口的IBIS-AMI 原理图

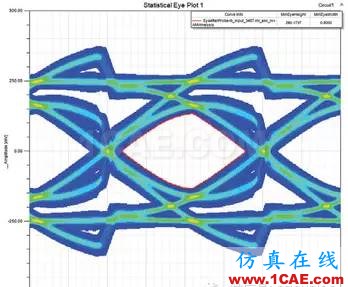

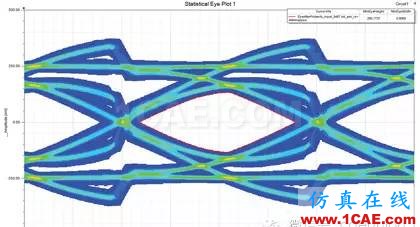

电路仿真器中所示的28Gb接口的统计眼图

频域仿真

在本项目中,该网络设备提供商为Interconnect Engineering提供了Allegro.brd文件格式的PCB设计。工程师把数据库导入到ANSYS Electronics Desktop,使用剪切子设计功能抽取相关通道,然后选择从半导体器件到光学模块的迹线。工程师随即根据组件规范创建端口激励,然后为半导体器件设置焊球模型和迹线的表面粗糙度模型,以增强保真度和精确性。然后工程师使用ANSYS HFSS运行频域仿真,为每一次迭代生成S参数结果。仿真在多台24核计算机上运行大约三天时间,因为求解器要剖分网格的面积很大。

ANSYS HFSS 3D 组件

该网络供应商利用仿真技术节省了数十万美元的成本和数月的开发时间。

工程师修改了通孔和反焊盘结构,重新布置了PCB层,以解决部分潜在问题。工程师随后又经过多次迭代,直至设计满足插入损耗(IL)和回波损耗(RL)规范要求。Interconnect Engineering的工程师考查了多种电路板替代材料并找到能够合理地满足插入损耗(IL)和回波损耗(RL)规范的最低成本材料。总体而言,Interconnect Engineering既找到了可放心删除以节省制造成本的地方,也找到了需要增加投入的地方,比如确保鲁棒性设计所需的背面钻孔。

时域仿真

同时还需要用于BGA接口器件和光学接收器模块的IBIS-AMI模型。这些模型都已导入到ANSYS Electronics Desktop中。工程师随后使用频域中产生的完整通道的多个四端口S参数模型的一个实例,创建电路仿真环境,从而开展时域仿真。眼图显示一个通道中存在问题,因此工程师重新配置了包括预加重、均衡、输出幅度、过程案例和电压设置等发射器和接收器设置,从而最大限度地增加眼图的开口。仿真完成后,眼图体现的误码率优于1x10-12(低于一万亿分之一),说明该通道符合时域要求。最后工程师检查频域,确保根据时域仿真做出的设计变更不会产生任何不利影响。

整个项目用了大约四个星期完成。在这段时间内,Interconnect Engineering研究了数十种可能的解决方案。该公司建议的设计能提供充足的正裕量,确保该通道能够在任何可预测的条件下工作,同时让实际的制造成本保持在低水平上。该网络设备供应商根据仿真结果构建了原型,其正如预期的一样工作。利用仿真技术得出的最终结果让网络供应商节省了数十万美元的成本和数月的开发时间。此外,网络设备供应商还得以把制造成本控制在或接近于可能的最低水平上,而且通过实现产品上市时间目标而挽回了客户关系。

相关标签搜索:利用仿真技术优化电路板设计 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析