T57 DDR5设计应该怎么做?【转发】

2019-03-15 by:CAE仿真在线 来源:互联网

感觉DDR4还没真正搞懂,DDR5就已经要来了,这就是我们所面对的生活,生命不息,学习不止……

就目前而言,DDR4支持3200 2DPC (2DIMM Per Channel)已经面临很多挑战,而DDR5的速率将是从3200 Mb/s起步,直至6400 Mb/s, 同样也是并行单端信号,同样也要支持2DPC,那么,在DDR5的设计中,什么样的技术可以在和DDR4拓扑结构类似的情况下,支持更高的速率呢?

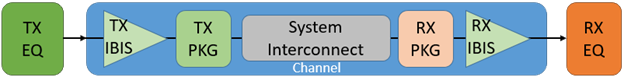

SERDES通道是点对点(point-to-point)的拓扑结构, 信号从最左端的TX通过传输通道传到最右端的RX,一般在终端会有很好的端接,而且不会有太多Stub的影响,对于整个通道的Loss也可以用低损耗的材料,EQ,Repeater等方式来很好的解决,而且差分信号对串扰的影响也会小很多。

而DDR是Muliti-Drop的拓扑结构,也就是经常所说的2DPC,对于Memory Down的拓扑结构,也就是把DRAM直接焊接在主板上的情况,CAC信号采用Fly-By的拓扑结构,会有更多的Load,那么,对于每一个DRAM来说,都会有从不同方向而来的信号反射,加之单端信号对串扰的抵抗力更差,对信号完整性的挑战就要更高。

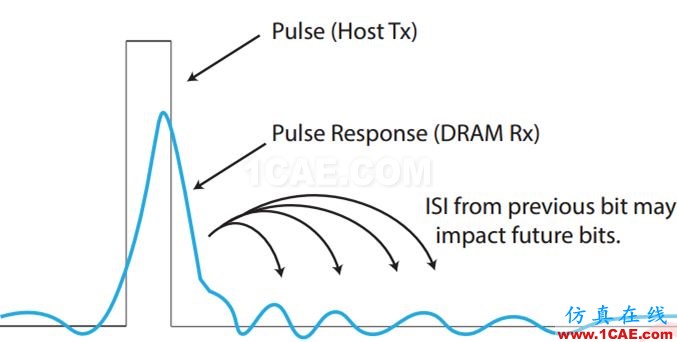

另外,一般而言,主板上的芯片控制器与内存相距不会太远,以免造成占用过多PCB面积以及可能造成通讯上的迟延,所以, 相对于SERDES信号,DDR通常是短且具有反射性的(Short but Reflective)通道, 也就是说因为阻抗于不同分支间的变化、再加上各RX端不同的termination, 会使得信号不断反射并形成很多的ISI干扰。

综上所述,对于DDR来说,最主要的问题,不是Loss, 而是由于反射引起的ISI。DDR信号速率一般要比SERDES低很多,但是到了DDR5以后,速率也有了明显提高,对于信号完整性设计来说,无疑具有更大的挑战。

目前来说,DDR5的很多规范还在定义当中,但是从主板PCB的设计角度来讲,DDR5的设计和DDR4并无特别明显的差异,也是采用并行总线的走线方式,同样采用2 DIMM per channel的设计架构,所以主要的设计差异在芯片设计和内存条设计。

SERDES之所以可以支持很高的速率,有很多方面的原因,但其中很重要的一个因素是均衡的应用,CTLE,FFE,DFE等等均衡技术,对提升SERDES的信号质量都起到了非常重要的作用,那么,对于DDR5来说,它们同样可以使用吗?使用效果如何?

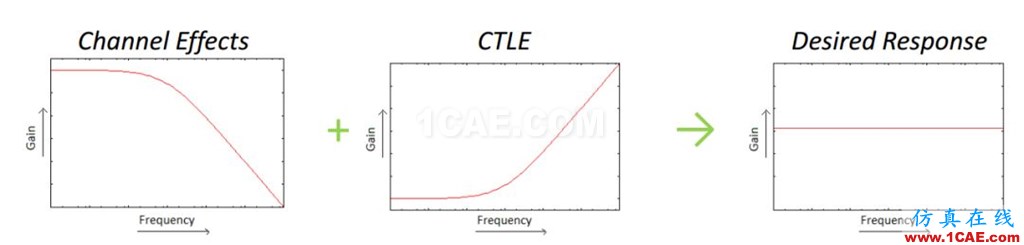

1. CTLE

CTLE主要通过增加信号中高频分量的幅度来抵消通道的衰减,使整个互连通道的响应变得平坦,有时也会通过低频段的衰减来进一步增强均衡能力。所以,CTLE对于长通道高衰减的SERDES会特别有效,但是相对来说,DDR对损耗并不敏感,而反射对它的影响更为明显一些,所以可以预见,CTLE在DDR上的应用将不会像其在SERDES上普遍且广泛。

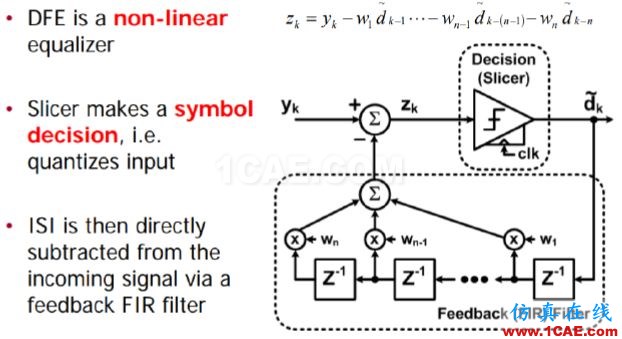

2. DFE

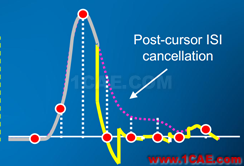

DFE是一个非线性滤波器,该滤波器使用之前检测到的符号来减去输入信号流的ISI,DEF经常用于消除由于阻抗不匹配而导致的信号反射所引起的ISI,而且不会放大噪声和Crosstalk,所以它可以应用在DDR上,但是DFE只能消除post-curson的部分。

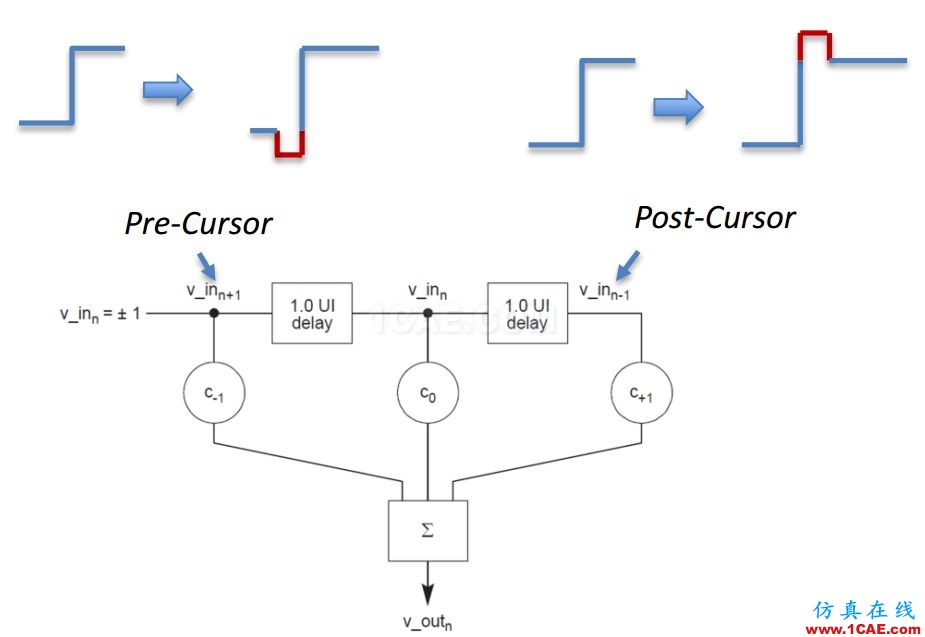

3. FFE

FFE是通过调整FIR滤波器各个抽头的系数来改变滤波器的频响特性,可以通过不同的系数组合来适应无源通道的衰减特性,对信号做加权以期能减小不同UI所形成的ISI影响。所以FFE在一定程度上来讲,对DDR也会有作用,但是FFE的tap及weight通常不能自适应,而且要消除ISI的影响,需要比较多的滤波器抽头,所以在实际应用中有所限制。

综上所述,针对DDR5的特点,DFE将会是一个很重要的解决方案。

DesignCon 2018有一篇文章“Equalization Requirements For DDR5 (By Nitin Bhagwath, etc)" ,其中对各种EQ对DDR5的影响做了比较详细的仿真和对比,将其结果拿来分享如下。

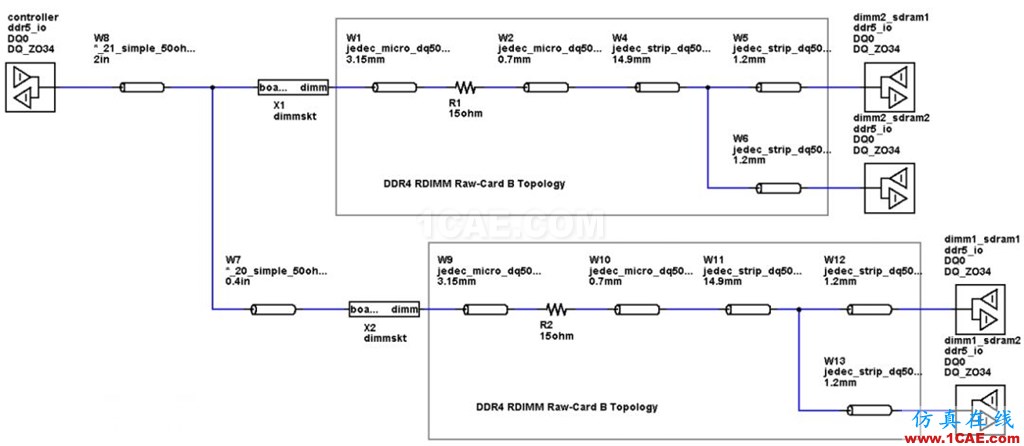

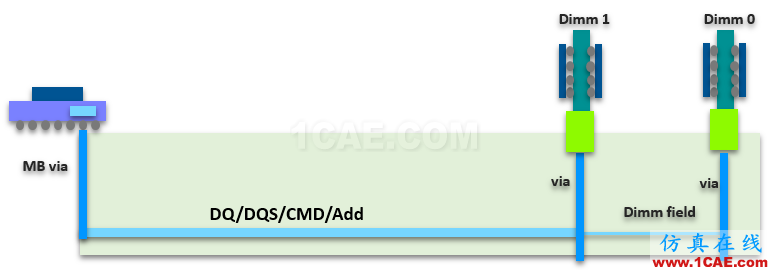

仿真拓扑:2DPC,两个DIMM, 每个DIMM有两个Rank,如下图(仅仅为示意图),DIMM1为Near DIMM,DIMM0为Far DIMM。

运行速率: 4400 MT/s。

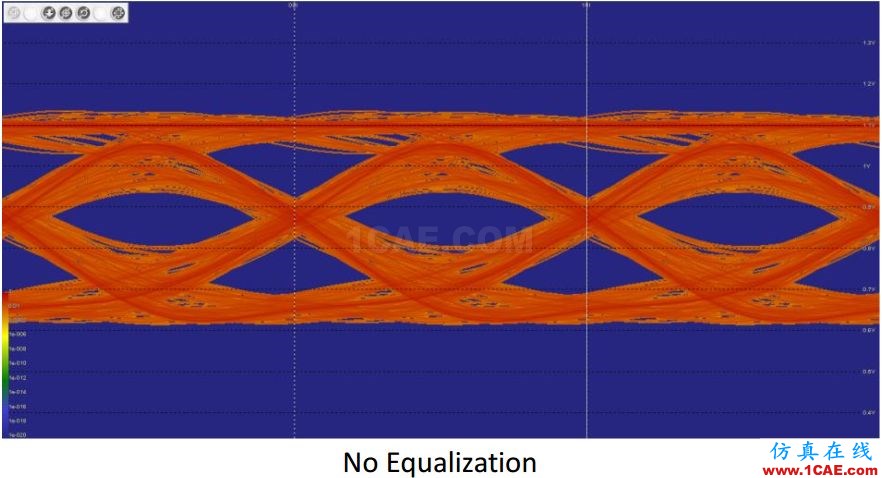

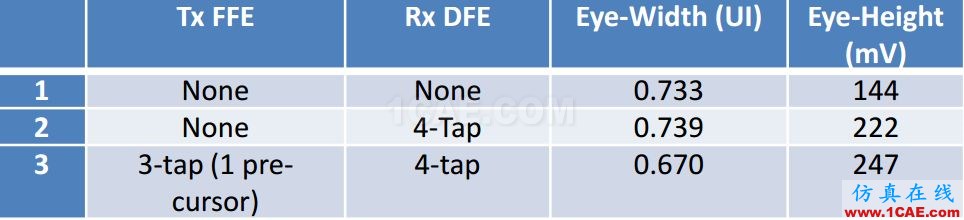

Case1: Write to Near DIMM:

如上示意图,当从CPU向DIMM1(Near DIMM)写数据时,DIMM0悬空,相当于一个长的Stub,信号相对比较差,所以在1个Channel 有2个DIMM插槽的情况下,如果只想插一根内存条,插在Far DIMM (DIMM0)会比较好。

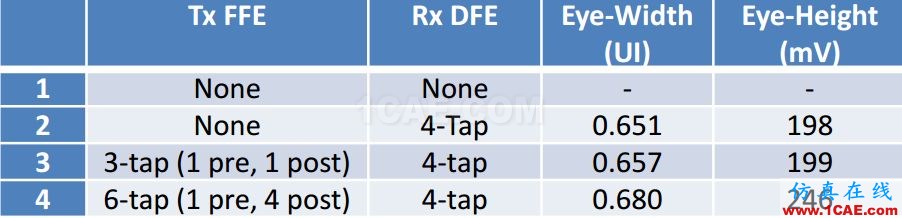

具体仿真结果统计如下:

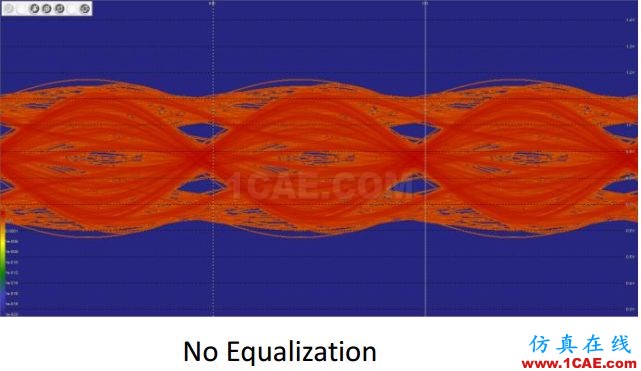

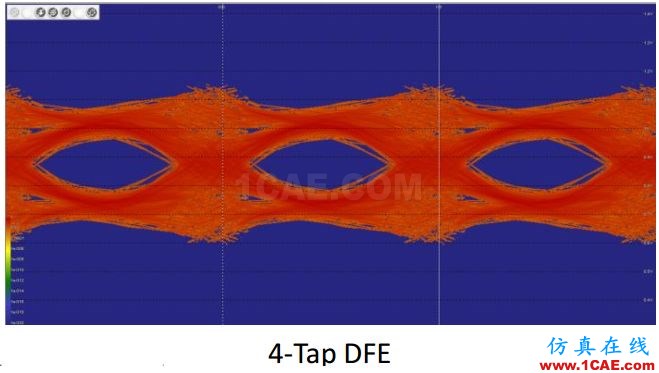

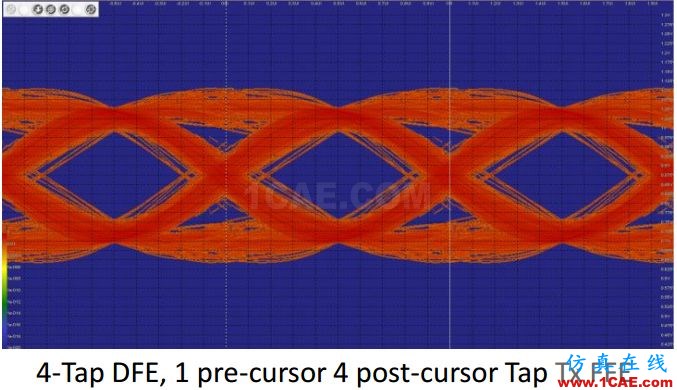

可以看到,DFE非常重要,没有DFE的话,眼睛完全睁不开,FFE对结果有提高,但是需要足够多的taps。

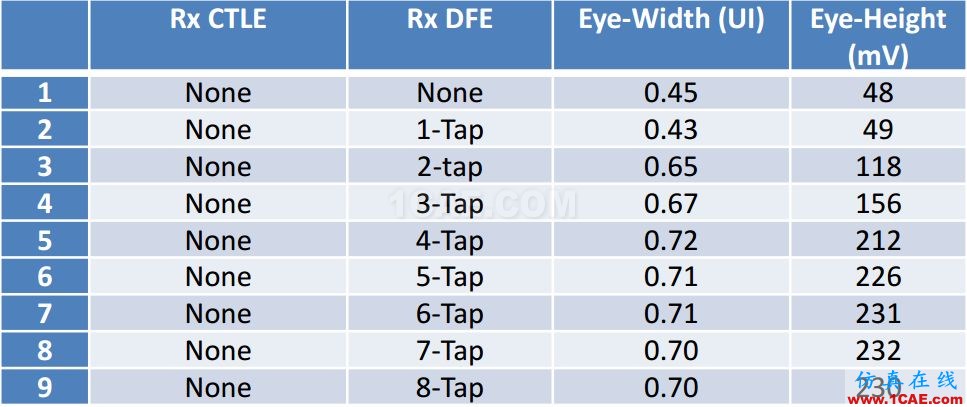

Case2: Write to Far DIMM

如Case1所述,Far DIMM情况下,Stub变小,所以Reflection减小,即使没有EQ,眼睛也是睁开的。

具体仿真数据如下:

没有EQ,眼睛也是睁开的,但是DFE和FFE依然可以提高信号质量。

Case3: Read from Near DIMM:

因为DRAM端基本已经确定,不会有FFE,所以此 仿真,假设DRAM端没有FFE.

DFE 4-Tap以后,对结果的影响就变的不明显。

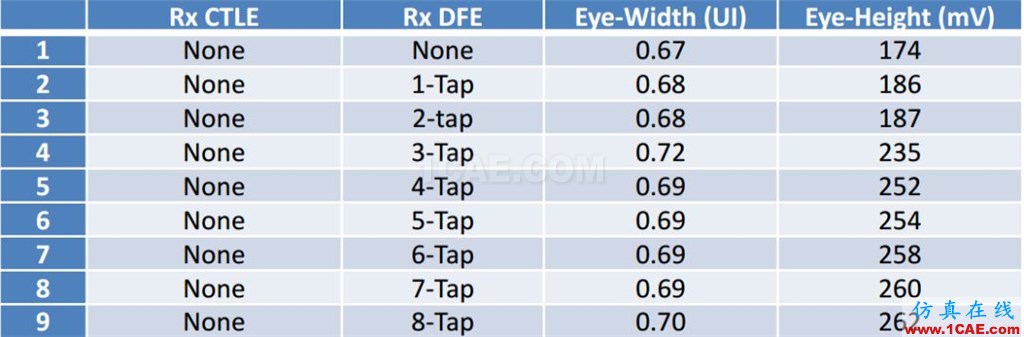

Case4: Read From Far DIMM:

可以看出,对DDR来说,4 Tap DFE已经足够。

DDR Channel是以Reflection以及由此引起的ISI为主要问题的Channel。DDR5信号速率提高以后,均衡是其非常重要的一个设计因素。

从仿真数据可以看出,DFE对提高DDR5的信号质量起到了很关键性的作用,FFE对其也有帮助,目前来说,DRAM端将会应用DFE,不会应用FFE,而Controller端,可以根据需要,看是否需要增加FFE。

当然,均衡可以减小由于反射引起的ISI,从而提高信号质量,但是却无法减小Crosstalk对信号的影响,而Crosstalk对DDR5的影响也很大,期待在不久的将来,会有新的技术来减小Crosstalk的影响。

-

N. Bhagwath, Arpad Muranyi, et. al. " Equalization Requirements for DDR5'' Designcon 2018

-

Stephen H. Hall, Howard L. Heck. "高级信号完整性技术”

相关标签搜索:T57 DDR5设计应该怎么做?【转发】 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析