DDR信号完整性仿真介绍(二)【转发】

2018-04-10 by:CAE仿真在线 来源:互联网

上篇文章我们对DDR做了一些基本的介绍,了解了DDR信号分组以及各组信号之间的长度匹配关系。那么,一般什么情况我们需要仿真分析呢?作者认为,多数情况下是我们的设计人员对这一块的把握不大的时候,因为DDR信号Net多,走线密度大,速率较高,DDR信号质量直接关系到整块板子的设计成败。

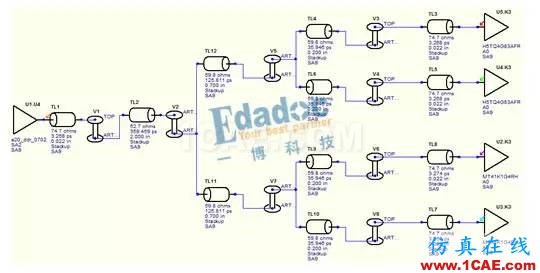

闲话不多说,本期将通过几个案例让初学者对DDR仿真有一个初步的认识。DDR信号仿真分为信号质量分析与时序分析,两者的侧重点不一样。下面来看看,某设计人员DDR3布线绕完等长之后,让我们仿真,拓扑结构如图1所示:

图 1

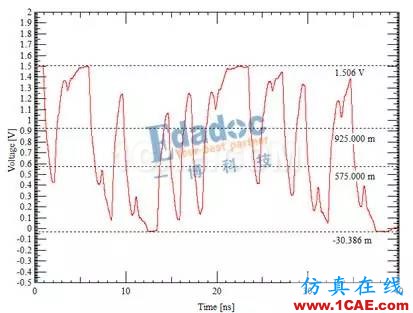

从拓扑结构来看,该设计是一个主控拖动四片DDR颗粒,采用T型结构。该设计分支等长做的都很好,貌似没什么问题,但是仿真出来的波形却是图2这样的:

图 2

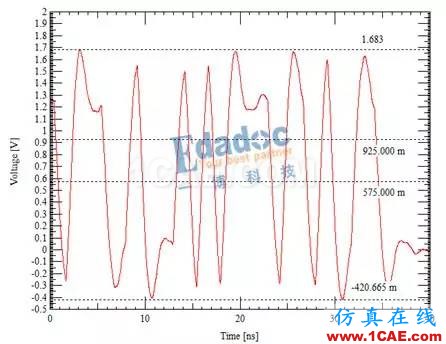

该波形电压虽然都通过了门限电平,但是裕量很小,波形也是参差不齐,显然不够理想。我们这里仅仅仿真了单根信号的质量,如果把串扰也考虑进来,波形就很难保证不出问题。作者以前也仿真过这种拓扑结构,但是波形没有这么糟糕啊。为了验证一下,作者把驱动芯片的IBIS换了,拓扑结构保持不变,结果得到的波形是这样的,如图3:

图3

图3信号质量与图2比起来要好一些,但结果不理想,过冲还是很大。其实这里,作者使用不同的IBIS模型,就是为了证明不同主控芯片输出的波形是不一样的。有时我们的Layout人员会有这样一个疑问,改版的时候仅仅只是换了一块主控芯片而已,PCB本身的布局没有改版,甚至芯片管脚对应的连接关系都没变,板子上的布线完全不用再改动了,这种想法是不对的,同一块板子,拓扑结构保持不变的情况,更换主控芯片,信号的质量也会受到影响的,这时我们的拓扑结构必须重新评估。

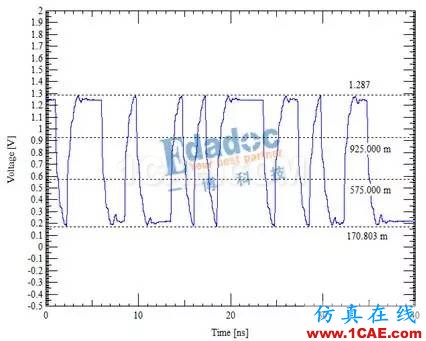

好了,造成图2与图3信号质量不好的原因是什么呢?经验丰富的网友们也许发现了,上面的T型结构没有做端接处理。同样,作者也发现了这个问题,结果加上端接电阻后,信号质量得到了改善,如图4所示:

图4

再来看一个DDR3设计案例,某设计人员在数据信号中加入了串阻,拓扑结构如下图5:

图5

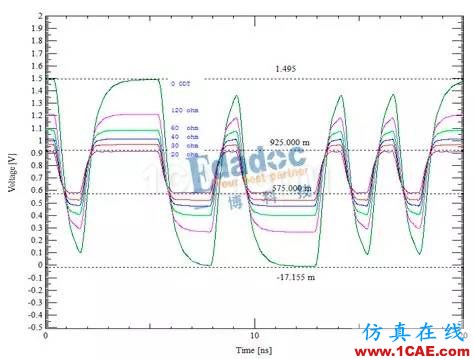

DDR3颗粒端有ODT功能,且有6种阻值可选,作者扫面这几种模式得到的波形如图6:

图6

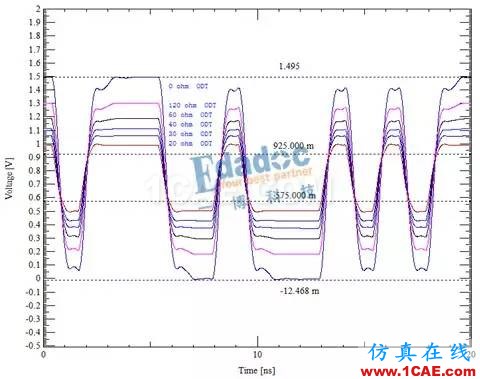

图6的波形,在开ODT的情况下波形裕量较小,DDR3本身带有ODT功能啊,为什么还要加串阻呢?于是我果断把串阻去掉,仿真波形如图7

图7

去掉串阻之后,波形的裕量更大了,且上升沿没那么缓了。所以,对于有ODT功能的DDR颗粒,布线时不用加串阻,这样不仅节省了元件,也节省了布线空间。

看来SI工程师是十分重要的哈,高速设计的成功离不开SI工程师的努力。拓扑结构的设计不是一劳永逸的,什么驱动芯片适合什么样的拓扑结构,需要仿真评估。仿真是一个不断尝试与探索的过程,它帮助我们找到互连与器件的最佳匹配。

ODT阻值选择与接收端电压幅值呈什么关系,为什么?

转自公众号:一博科技高速先生 作者:袁波

相关标签搜索:DDR信号完整性仿真介绍(二)【转发】 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析