DDR3布线的那些事儿(一)【转发】

2017-10-13 by:CAE仿真在线 来源:互联网

问答对于DDR3的布线我们应该注意那些问题呢?

下面我们以64位DDR3为例 :(注意:设计要求会因为芯片公司而有差异,具体以芯片手册要求的为准。)

首先是数据线,数据线分组如下:

GROUP0:

DQ0-DQ7,DQM0,DQS0P/DQS0N;

GROUP1:

DQ8-DQ15,DQM1,DQS1P/DQS1N;

GROUP2:

DQ16-DQ23,DQM2,DQS2P/DQS2N;

GROUP3:

DQ24-DQ31,DQM3,DQS3P/DQS3N;

GROUP4:

DQ32-DQ39,DQM4,DQS4P/DQS4N;

GROUP5:

DQ40-DQ47,DQM5,DQS5P/DQS5N;

GROUP6:

DQ48-DQ55,DQM6,DQS6P/DQS6N;

GROUP7:

DQ46-DQ63,DQM7,DQS7P/DQS7N;

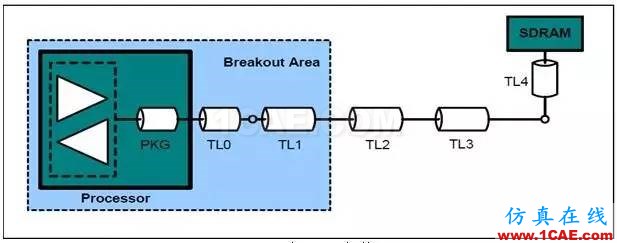

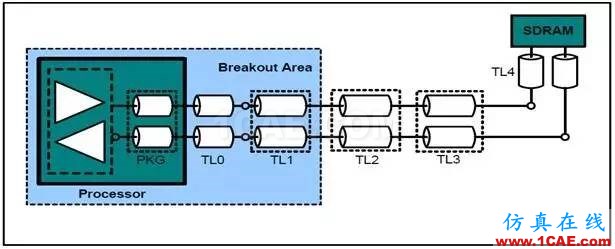

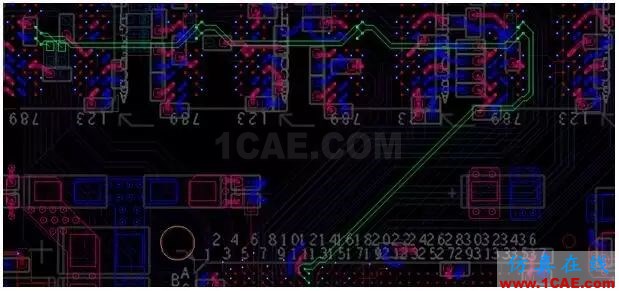

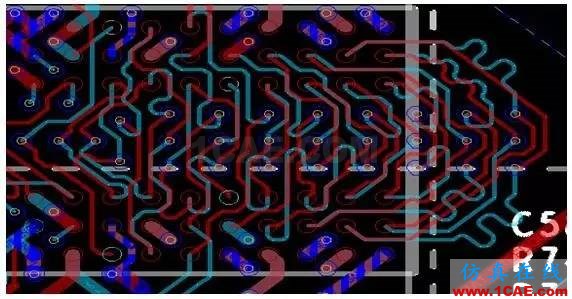

数据线其拓扑是点对点的形式,拓扑如下所示:

图1:DQ拓扑DQS拓扑如下:

图2:DQS拓扑

数据线布线注意事项:

1.同组同层,如:GROUP1,同一组数据线要走在一起,并要走在相同层面; 所有的数据线优先考虑以GND平面为参考平面;

2.走线间距:组内按3H(说明:H指的是到主参考平面的高度,本文中所使用的间距为中心间距)原则;组间间距要5H以上;DQS和DQ的间距按5H设计;

3.DQS等长:对于DQS差分线的线间距要小于2倍的线宽(紧耦合设计);差分对内长度误差控制在5mil以内; 组内等长以DQS为基准,等长控制在20mil以内且尽可能的即时等长;

4.数据线在满足和时钟的时序关系外,还需注意最长的长度要求(例如Intel Romley要求不超过6500mil),具体的以芯片手册要求的为准;

而对于控制线、地址线、时钟线 分组如下:

GROUP8:Address ADDR0-ADDR14 共15根地址线;

GROUP9:Clock CLK、CLKN差分对;

GROUP10:Control 包括WE、CAS、RAS、CS0、CS1、ODT0、ODT1、BA0、BA1、BA2等;

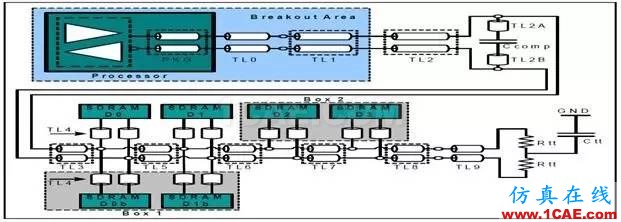

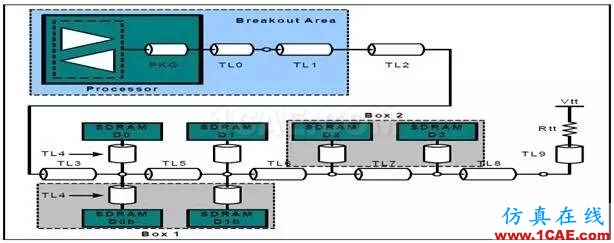

图3:时钟地址、控制线拓扑参考图

图4:地址、控制线

对于拓扑结构一定要看芯片是否支持读写平衡(Read and Write Leveling)。

如果不支持和DDR2一样按T拓扑处理。(保证CPU到DDR各支点等长,注意终端电阻要接到最大的T点上)

支持读写平衡情况下:

2-4片颗粒:走T点或是Fly-by都可以;

4片及以上颗粒:建议走Fly-by。

下面是4颗粒DDR3按T和FLY-BY 拓扑结构的实例:

图5:4颗粒T型拓扑处理方式

图6:4颗粒FLY-BY拓扑处理方式

而对于FLY-BY的拓扑结构 ,要注意以下几点:

1. 间距 组内按3H(说明:H指的是到主参考平面的高度,中心间距3H,)原则;组间间距要5H以上;CLK和ADD/CMD等的间距按5H设计;

2.尽量同组同层完成走线且有完整参考平面(GND/power);3.各个DDR颗粒间的走线,尽量用COPY,长度误差在20mil以内(推荐5mil);若因结构限制,最大不能超过100mil;

4. 时钟线推荐带状线布线以(GND/POWER为参考平面); 时钟要紧耦合设计,对内等长控制在5MIL以内;源端和终端匹配的走线,长度不要太长(推荐300 mil以内)

5.终端(上拉)电阻要放在最后一个DDR颗粒(末端),且走线长度小于500mil;

6.在有多个负载时,为了减少串扰和加大负载容性补偿,到第一个颗粒(主干道)的走线阻抗可以比到后面的走线阻抗偏小点,5-8欧姆左右。7.Add/Com/Ctrl/Clk网络从控制器到第一个DDR颗粒的走线长度不要超过6000mil,到最后一个DDR颗粒不要超过12000mil。

8.在多个考虑表底贴时分支的节点走线长度小于200mil且尽量等长.

图7:表底贴T型拓扑处理方式

本期对于DDR3的布线要求先说到这里,对于设计中还有那些重点需要关注和设计的我们将在下期继续讲解。(以下内容选自网友答题)1.电源稳定性,器件布局与后期布线都会影响电源纹波; 2. 线宽、线间距(组内/组外),此部分也影响阻抗; 3. 叠层考量,布线规划好,综合考虑在哪层走线; 4. 板材考量; 5. 串扰反射的考量; 6. 过孔的考量; 不同的布局布线都会影响上述参数

线宽线间距,绝对长度相对长度,拓扑结构,叠层参考面走线规划,过孔等等,总之各种考量是为了满足时序,信号质量,速率等要求@二羔子评分:3分1、一个字节内的8位数据线同层布线,参考完整的电源与地平面。dqs差分走在数据线中间,以dqs为基准做10mil的等长。数据的字节间8位可以不用等长。2、布线3w,且时钟和dqs差分与单线控制5w间距。3、阻抗主线按40欧,ddr端按60欧,差分按85欧。低阻抗为了更好的阻抗匹配减少反射。4、地址命令控制从控制器到每片ddr控制误差20mil,参考完整的电源与地平面。5、vref走线20mil,远离vtt电源,vtt铺铜过流3.5A。@刘栋评分:3分一、对于地址和控制时钟线,确认控制器是否支持writing leveing,支持的话对于一驱二及以上优先采用fly-by拓扑走线,不支持的话T型拓扑走线。二、数据都是点到点的结构,优选同一组数据走在同一内层,便于控制阻抗。三、对于参考面,优选地平面,满足不了,只能参考自己的1.5V IO电源平面。四、为了控制SSN,建议按2W及以上间距走线。五、时钟线和DQS线距离其它走线尽量保证3W及以上。六、根据时序要求控制等长。@杨勇评分:3分

以上三位基本都回答到了(3分)注意布局首先,终端匹配电阻尽量靠近ddr3并且尽量靠近主控芯片,布线要遵守3W原则,注意电磁兼容性,做好电容滤波,电源要注意io和内核电源以及vtt等要尽量隔离做好相互防止干扰问题@ zhl评分:2分首先,确认走线结构,fly-by orT型; 其次,确认阻抗大小,设置叠层线宽线间距等,并根据走线结构设置线组规则; 最后,信号线尽量同组同层,线间距至少2w,时钟线要3w以上,且参考面完整。@ 铜钱评分:2分总体规则:vref的电容尽量靠近管脚放,vtt的电容尽量靠近端接电阻放,信号相邻层必须有地平面,不允许跨切割,信号需控制阻抗,所有信号尽量最多经过2次过孔,芯片端尽量多打地孔。 数据线:总长尽量小于2000mil,DQS差分对的过孔尽量遵循g-s-s-g,数据单端线间距尽量控制在2.5倍线宽以上,每组数据线必须在同一层。 时钟线:尽量使用fly-by结构,端接电阻放在fly-by结构末端,stub尽量小于200mil,并且分支线的stub等长且小于50mil,过孔尽量遵循g-s-s-g,时钟线与其它线间距应三倍差分间距以上。 地址控制线:尽量使用fly-by结构,端接电阻放在fly-by结构末端,stub尽量小于100mil,并且分支线的stub等长且小于50mil,线间距1.5倍线宽以上。@杆评分:2分

以上三位的回答也比较好, 2分1,定好参考面,选择噪声小的电源平面或地平面,如有demo板参考demo板要求。 2,同组信号尽可能同层走线,不要跨分割。 3,地址线和控制线注意与时钟信号的等长约束。选通信号与同组信号的等长控制。非fly by走线的还注意时钟与选通信号的等长约束。 4,减少串扰,走线满足3w原则,同参考层的相邻层走线垂直。 5,减少电源躁声,ddr3和vtt的电源走线尽量短而粗。 6,走fly by走线需要提前注意主控芯片是否支持读写平衡。@hk评分:3分首先要确定片子个数,用于确定布局和拓扑结构,其次是各外围元器件放置位置(文章已经讲得比较详细了),然后设置线宽,线距,线等长,最后注意走线的技巧(以前文章也讲得很多了,不外乎保证阻抗的连续性和参考平面,电源的连续性)。@大海象评分:3分1.信号组中,同组同层,DQ以DQS差分线为参考,等长设置在10mil。2.地址/控制/命令组,若主控芯片支持读写平衡,使用Flyby结构,尽量减少Stub长度。若不支持使用T型拓扑结构。阻抗补偿有利改善信号质量,单端40-50欧,差分85-95欧。3.时钟差分线在同层,参考地平面,保持平面完整,长度控制在25mil误差。4.线宽线距满足3W原则,防止干扰。蛇形走线间距大于25mil。5.信号线不能跨分割电源平面。6.VTT电源使用铺铜或平面连接,宽度大于150mil。@山水江南评分:3分1、DDR3要严格控制阻抗,单线50ohm,差分100ohm,差分一般为时钟、DQS。在走线过程中,尽量减小阻抗跳变的因素,比如:换层、保证参考平面完整不跨分割、线宽变化、避免stub线等。2、为满足DDR3时序,需要将DDR3信号分组走线。数据线每八根一组,外加相应的DQS和DQM走线必须同组且保证同层,换层次数一致,长度误差控制在±10mil内;3、地址线、控制线、时钟线分为一组,长度误差控制在±25mil内。4、布线要求同组同层,最好都参考地平面。时钟对内等长要小,两根线误差小于5mil。时钟与其他信号线之间距离最好大于15mil其它信号线之间在有空间的情况下保证线间距3W,局部区域可适当减小距离。以减小信号之间的串扰。5、DDR3地址线、控制线、命令线FLY-BY的走线方式,以提高信号质量。采用FLY-BY设计,可降低同时开关噪声(SSN) 。当系统 DDR 的个数大于 4,布线长度大于 2 英寸,强烈建议加上端接电阻。 RS 和 RT 的值取决于驱动强度等,需要仿真和架构测试来优化。@ 龙凤呈祥 紫红龙骧评分:3分

以上几位基本把所有需要注意的重点都基本回答了( 3分)1.减少串扰:走线保证3w或以上的间距,相临层走线不重叠,同组数据线走同层,不跨分割 2.减少电源躁声:ddr3和vtt的电源模块,尽量靠近负载,电源层与地层间距尽量小 3.注意容性负载带来的阻抗不匹配问题,调整主段线宽(加大线宽,减小阻抗) 4.检查主控是否支持读者平衡,支持才能用fly-by,否则采用ddr2的拓扑。@Ben评分:3分DDR3布线的注意事项: 1、注意不支持读写平衡(Read and Write Leveling)功能的DDR3主控芯片,不能采用Fly-by结构; 2、布线时推荐按照数据组、地址命令组、控制组、时钟信号、电源的顺序进行; 3、根据Datasheet,布线要满足线宽、线距及阻抗的要求; 4、保证信号完整性,走线不要跨分割;避免走在参考平面的边缘上,尽量离边缘有一定距离(比如至少30mil以上); 5、各数据组信号,同组信号要走在同一层,至少保证参考同一平面。@ly评分:3分1、控制阻抗;2、如有多颗需要确定布线拓扑结构;3、尽量满足3W原则;4、VREF电源线尽量不小于20mil宽度;5、参考面尽量是GND或者DDR3电源的平面,避免其他电源的平面。6、数据组,地址、控制、时钟组做好等长等@Jamie评分:3分1.整体策略考虑。若制板要求允许,可考虑 DDR 芯片正反面重叠放置,以利于布线;建议DDR区域与其他非DDR区域相对隔离,DDR区域内不要放置其他元器件,非DDR信号走线不要进入DDR区域 。2.将DDR信号分为clock,data, address/command/control三个组。每组分别有不同的设计规则。A) clock 组:为差分对时钟信号,走在完整的GND 平面相邻的信号层;原则上所有时钟应走在同一层;避免时钟交叉,必要时可以调整时钟到不同 DDR 芯片的连接;时钟长度相等,误差控 制在20mil内,时钟长度等于或略大于地址信号。B)data 信号应尽量走在GND平面相邻的信号层;每个lane的信号走在同一层相邻lane的信号在不同层;mdqs信号间距至少4倍线宽(20mil)。与非DDR信号之间的距离至少20mil;每个lane 内信 号线等长,长度差控制在 25mil 内;lane 之间信号的长度差控制在 25%。C)ADDR/CMD/CTRL组,要求该组信号线采用fly-by型拓扑结构。3.DDR 电源。电源输出后过滤波网络;电源线要宽,Vref至少25mil,Vtt至少 150mil, 如可能尽量铺成平面;尽量远离信号线,至少20-25mil电源反馈Vsense应接在Vtt线(平面)的中间点。@Lee评分:3分

以上四位网友回答很全面 (3分)1、时钟线要做差分100欧阻抗控制,误差小于5mil,2、数据线要做等长控制,误差范围小于50mil,布线在同一层,至少dq在同一层3、地址、控制、命令信号线做等长控制,误差范围小于100mil,4、地址线阻是否能走flyby要看芯片要求@涌评分:2分

这位网友回答也对了,给你满分怕你骄傲,继续加油,哈哈~ (2分)感觉这次问题好宽,好难说完整,提一下常见的经验规则(1)建议线宽和间距不能小于4mil;时钟信号线严格等长,偏差范围50mil以内,且长度应尽量小于4inch,信号线走线等长处理时应当注意芯片基板上的DDR信号走线长度,然后才在外围进行补偿等长处理。(2)注意板层,单端走线阻抗建议参考DEMO,差分严格控制在100Ω(±10%)。(3)信号走线邻近地平面,避免电源与地分割,保证完整参考平面;走线尽可能短,路径上少点过孔,保证阻抗连续性;不可避免换层时走线时注意地通孔完善信号回流路径。(4)相邻信号走线距离保持在2-3倍线宽。(5)避免时钟信号紧邻数据、地址总线,避免地址信号紧邻数据信号。(6)DDR3信号与非DDR3信号之间走线间距至少20mil,且包地处理。(7)Vref脚要加去耦电容,且走线尽量宽,与其他信号线建议20mil-25mil间隔。(8)电源上,Vref注意与其他电源隔离,最好包地屏蔽处理,且不能作为其他信号线的参考平面。(9)VTT信号必须通过带状铜皮走线,尽可能靠近DDR。(10)如果使用了排阻,同一个排阻上的信号必须属于同一个DDR信号线组,尤其避免DQS与地址/控制线分布在同一个排阻上。@ Garyee评分:3分DDR3布线注意事项: 1.根据芯片是否支持读写平衡,决定是否采用Fly-by还是T拓扑。 2.阻抗要求:单线50欧姆,差分100欧姆。 3.DQ信号,分组,同层,等长,以GND作为完整的信号回流层。线距3w以上,控制串扰。 4.地址线,控制线,时钟线等长,以VDD作参考平面。线距3w以上,控制串扰。 5.电源处理。@王萍

评分:3分

转自公众号:一博科技高速先生

开放分享:优质有限元技术文章,助你自学成才

相关标签搜索:DDR3布线的那些事儿(一)【转发】 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析

编辑