如何解决高速电路信号过冲的问题

2017-05-21 by:CAE仿真在线 来源:互联网

如何解决高速电路信号过冲的问题

1,什么是过冲?

当较快的信号沿驱动一段较长的走线,

而走线拓扑上又没有有效的匹配时,

往往会产生过冲。过冲带来的问题主要是“1”电平高于接收端器件的输入最大电压值(VIHmax),或“0”电平低于接收端器件的输入最小电压值(VILmin),这样可能给器件带来潜在的累积性伤害,缩短其工作寿命,从而影响产品的长期稳定性。

2,解决过冲的一般方法是匹配,或叫端接(Termination)。匹配的中心思想是消灭信号路径端点的阻抗突变,归纳一下,无非可以总结为

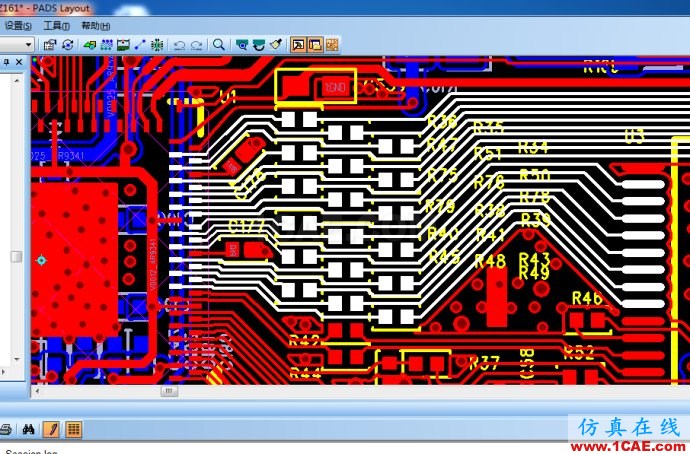

两种形式:源端的串行匹配(如下图的PCB所示),用于消灭二次反射,以及终端的并行匹配,用于消灭一次反射。不是每种匹配方式都适用于任何场合,例如,50ohm并行匹配一般不用于LVTTL/LVCMOS等电平逻辑,因为电阻上消耗的功耗大得难以接受;除了匹配之外,还有另外一种改善过冲的行之有效的方法,那就是令驱动端的信号沿变缓,使得原先的高速信号变得不那么“高速”。使信号沿变缓的最常用的手法,就是降低驱动器的驱动电流。这种手法在FPGA/CPLD设计中尤为常用。

两种形式:源端的串行匹配(如下图的PCB所示),用于消灭二次反射,以及终端的并行匹配,用于消灭一次反射。不是每种匹配方式都适用于任何场合,例如,50ohm并行匹配一般不用于LVTTL/LVCMOS等电平逻辑,因为电阻上消耗的功耗大得难以接受;除了匹配之外,还有另外一种改善过冲的行之有效的方法,那就是令驱动端的信号沿变缓,使得原先的高速信号变得不那么“高速”。使信号沿变缓的最常用的手法,就是降低驱动器的驱动电流。这种手法在FPGA/CPLD设计中尤为常用。

源端串行匹配PCB设计案例

3,振铃:过冲往往伴随有振铃,或者说,过冲是振铃的一部分。振铃产生的第一次峰值电压,就是过冲。之所以要将二者区分来讲,是因为振铃的危害除了过冲外,还有其产生的电压波动可能多次跨越逻辑电平的阈值电压,使得接收端产生误判,对于CMOS器件来说,振铃过程中还可能使得上、下MOS管同时导通的时间延长,急剧地增加功耗,影响器件寿命。既然振铃和过冲的产生机理一致,对它的处理方式也就和处理过冲无异,这里仅作简要的理论阐述。

开放分享:优质有限元技术文章,助你自学成才

相关标签搜索:如何解决高速电路信号过冲的问题 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析

编辑