信号完整性设计中的5类典型问题

2017-05-11 by:CAE仿真在线 来源:互联网

今天咱来扒一扒工程设计中关于信号完整性的那点事,Bala一下工程设计中常遇到的5类典型问题。没有因为这些纠结过的,应该还没开始做SI设计。相信在一线摸爬滚打的工程狮看了会有共 鸣!

第1类问题:必须依靠仿真的问题

有些问题,第一次设计时,如果不依靠仿真,没什么好办法知道到底行不行或者有没有危险。举一个常见的栗子:一拖多拓扑结构,这是一个出现概率很高的设计场景。假如有一个主控板,通 过背板(有些公司叫底板)拖6块板卡,如果是第一次设计,那怎么评估这个方案行不行!靠设计规则?靠经验法则?靠猜?那纯粹是撞大运。当然有些人会说了,打一板试试就知道了。当然可以,但是像这种系统级的方案, 打板一次费用和周期都几乎不可接受(当然土豪除外)。要提前评估方案的可行性,理论分析是少不了的,但这个问题仅靠理论分析搞不定。

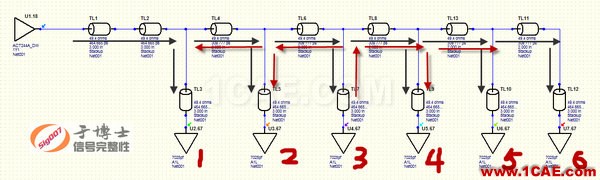

咱先从理论上看看这个拓扑中会发生什么。芯片的input buffer对信号来说通常表现出很高的阻抗,信号传输到接收芯片会发生反射。下图中6个接收端都会有反射。反射回来的信号遇到走线 分叉会分别进入两条岔路,比如从3反射回来的信号沿主干线向左右两个方向传输,传到1、2、4、5、6等接收器时再次发生反射。也就是3反射的信号会干扰其他芯片的接收信号。同样的,其他任何一个接收器的反射信号都会 干扰别的接收器。反射过程会发生很多次,延时叠加,反复的反射震荡,这是一个很复杂的过程,理论上简单,但最终会叠加出来一个神马东西?想不出来,得靠软件。

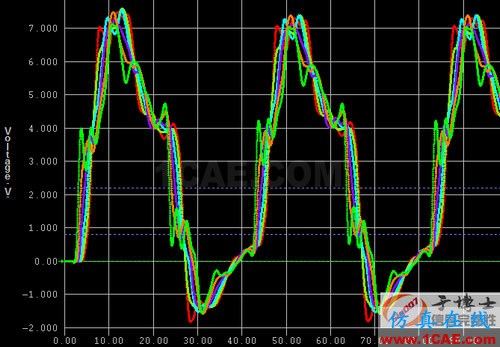

如果不做任何处理,波形长啥样?简单的仿真就能发现明显的风险,见下图,高低电平冲得太厉害了,有隐患。

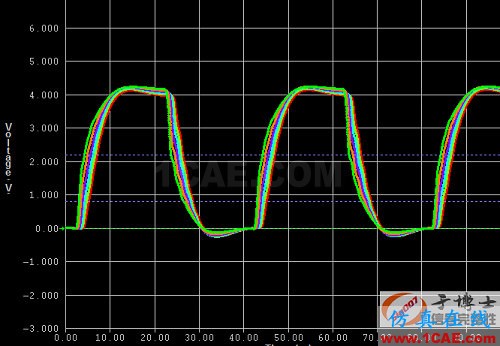

通过简单的处理,消弱反射信号在各个接收器之间反复反射震荡,我们可以把波形搞成这个样子。这下放心多了。类似这种需要仿真的问题很多,通过仿真规避风险效果很好的。

第2类问题:无法仿真或很难仿真的问题

仿真是信号完整性设计很有效的手段。仿真软件很神奇,迷倒了一大批工程师。

如果这个东西真这么简单那就太好了,click、click、click...,OK,完活,多爽!

哪有如此美妙的世界!

过于依赖仿真,干活时候会经常遇到纠结痛苦的事。尤其把自己定位成仿真工程狮的,面对问题,有时候会无处下手,不知道该仿什么。真要遇到这种事,就该好好考虑一下了,有些事不是仿 真能搞定的,也许你遇到的是这第2类问题。

比如下面这个栗子,很酸爽,但绝对没有糖炒的好吃。

有些单板上会有个别时钟信号对抖动要求非常高,如果这个时钟抖动大了,误码测试就不过关。高速串行接口对时钟都是有要求的,我们看下典型接口信号抖动构成,时钟信号的抖动对传输信 号的抖动贡献是不能忽略的。那么问题来了,硬件人员把这个问题丢给你,怎么解决无所谓,硬件要的就是结果,搞定就行。那你怎么搞定这个事?靠仿真么?怎么仿?仿什么?

开工之前,分析一下那些因素会影响时钟的抖动,先列张主要因素的清单:

1、反射(万恶的反射,哪都有它)

2、串扰(万恶的串扰,哪都有它)

3、模态转换(有影响要注意)

4、参考平面(隐藏的雷区)

5、差分对设计(被很多人忽略的)

6、时钟芯片的电源(重头戏)

7、层叠结构安排走线层安排(一念之差的变数)

8、提供时钟的晶振选型(硬件选型会慎重的,通常不用SI人员处理)

9、晶振电源的处理(不可忽略)

其他Layout相关的细节就不说了,单单上面提到的这些就够仿真工程狮喝一壶的(整点二锅头还是伏特加?)。

好吧,仿真工程狮,仿真工程狮,咱开仿。打开神奇的软件,然后呢,没然后了........。往软件里面塞什么内容让它跑仿真?

那个什么,电源对抖动的影响,仿真肿么破?那个参考平面的影响,仿真肿么破?从仿真的角度来做头疼是必然的。但是如果你换一个角色,以信号完整性设计工程师的角度去看会豁然开朗。 该仿真的仿真,仿不了的设计上控制一下不就可以搞(tou)定(lan)了。反正最终要的就一个结果,抖动降下来就OK。

黑猫白猫抓住耗子是好猫。好产品是设计出来的,不是仿出来的。不纠结,做好猫!

第3类问题:需要仿真但仅靠单一的仿真手段还不行

举个典型栗子......。咳咳,又是栗子,够了,被拍飞........。

好吧,鼻青脸肿的咱回来接着说。电源的磁珠滤波(又是万恶的磁珠滤波),话说电源上用磁珠滤波那是比比皆是,话说这个磁珠滤波吃掉了多少硬件人员的加班时间,调试调试再调试,调试 到崩溃。咋能偷点懒呢?

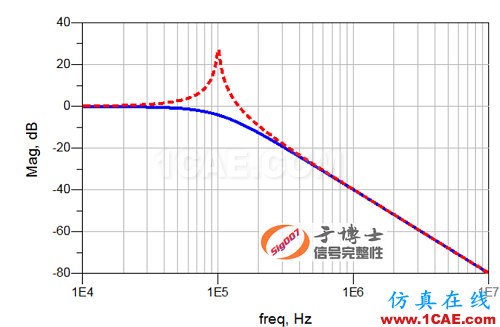

拿来神奇的仿真软件,click、click、click... ... ...OK。三下五除二整出了下面这个漂亮的频响曲线,蓝色的那条是设计好的。怯怯地说一句,偷懒了,直接拷贝的老图,没重新做图,直 接被拍飞........。

完工了?真的完工了吗?呃,别高兴太早,一大群邪恶的Bug正在排队赶来准备挖坑呢。象下图这样,磁珠和电容后面拉出来的那条小尾巴,你把它放哪里?拉多长?

拉线太长了肯定不太好,地球人都知道。试想一下,如果这个小尾巴刚好通过电路板入口电源铜皮正上方会怎样?

所以相邻的平面层要考虑,如果你把它放在表层,那它下面紧邻的平面层最好是GND。如果安排在内层呢?内层电源平面层往往被分割的很乱,如果这种磁珠滤波器用的比较多,那可能放不下 。平面层放不下就得放信号层,问题又来了,夹在上下两个平面之间,而且旁边会有其他信号线。这都是坑,要小心处理。

这个问题仿真能解决磁珠和电容的选型问题,规避那些坑就不能靠仿真了,只能Layout时,认真进行设计控制。

第4类问题:需要进行风险监控的细节问题

有句老话怎么说来着?魔鬼隐藏在细节中!对,是魔鬼,绝对是魔鬼!不少魔鬼会让你不得不激情高昂的去加班去返工。

PCB是一个立体结构,不要总用平面思维去看待PCB。不罗嗦,上图,自己看。俺课件中摘出来的图片,话说每次讲课这张图我都会讲好长时间。

第5类问题:需要Layout前整体规划的问题

不罗罗索索的说教了,整的跟个唐僧似的招人烦,和老于一起重温一下很久以前经历的一件事。历史上的某天,某君打来电话,给老于出了道难题,酱紫的......。

某君:于博士,我有块板子要投板,有点不放心,想让你看看行不行。

老于:啥情况,说说!

某君:板子上有10G差分接口,有DDR3。

老于:10G是单lane的还是接口的......。

某君:单lane。

老于:好,知道了,你继续。

某君:我把10G差分对走在了靠近top的几个内层,DDR3信号线走的是靠近bottom的内层。

老于:咋不把10G差分对放在靠bottom的内层?有风险,调一下走线层吧!

某君:差分对线宽线距定了,要调到下面几层,阻抗没法控制100欧......

老于:你DDR控制到40几欧?

某君:是。

老于:和板厂沟通,重新定一个层叠就行了呗,这不费多少精力。

某君:层叠都定好了,不能改了。

老于:打下背钻吧。

某君:BGA下的孔太小,怕不安全。

老于:... ...

好纠结的困局,这点事如果画板子之前整体做个规划,哪些信号走哪个信号层,哪个平面层放GND,哪个平面层放电源,也就没这么纠结了。

本来没坑,自己给自己挖了一个。

类似问题还有很多,别小看这个,整体规划可以规避很多不必要的麻烦。

相关标签搜索:信号完整性设计中的5类典型问题 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析