高速数字电路AC耦合电容HFSS仿真

2017-04-17 by:CAE仿真在线 来源:互联网

高速数字电路AC耦合电容HFSS仿真

高速数字电路中我们经常会需要耦合电容,特别对于一样高速SERDES,往往都需要进行AC耦合,一些时钟线也有可能需要AC耦合,这个时候不可避免的需要使用到耦合电容,我们知道高速数字电路中,需要尽可能的保持传输线的阻抗恒定,减少信号反射,提高信号质量,但是AC耦合电容的引进必然会导致阻抗的不连续性。

耦合电容引起的阻抗不连续的原因是:电容焊盘相对于导线过大,根据公式C=εS/4πkd,能够得知焊盘和参考层之间的寄生电容会增大,传输线的特性阻抗与寄生电容大小成反比,所以AC耦合电容处的阻抗就会相较于导线处变小,就会引起信号质量变差。

因此为了减小电容焊盘出的阻抗不稳定,我们可以对焊盘进行优化,可以想象到。如果增大焊盘到参考面的距离,那么寄生电容就会减小,阻抗就会增大,所以一般高速数字电路中,一般都会对电容焊盘下面的参考面挖空,让电容焊盘参考更下面一层的参考面。

传统的2D阻抗计算软件是没法进行AC耦合电容焊盘仿真的,必须使用3D电磁仿真软件,一下介绍HFSS的仿真。

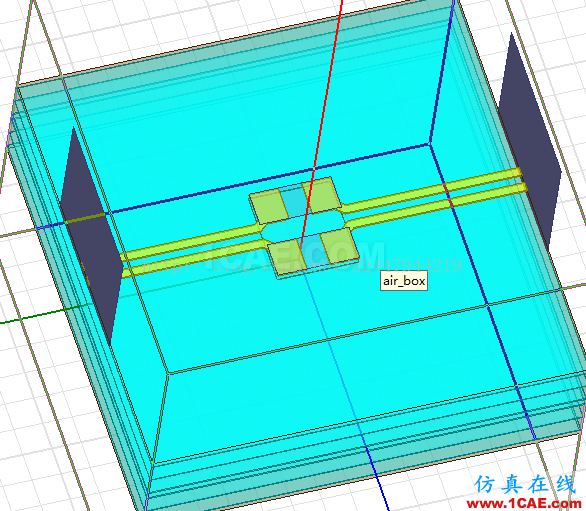

HFSS仿真电容,首先肯定需要进行仿真模型建立,可以参考我之前过孔建模的文章或者上网上找一个基础教程,电容仿真对于初接触者,最麻烦的是电容该怎么建模,下面介绍一下。

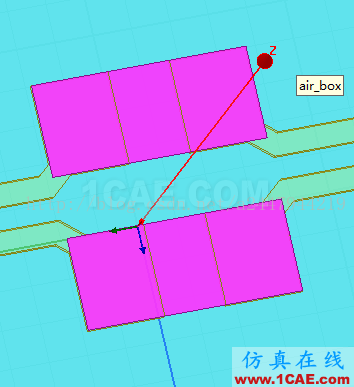

HFSS里面有各种各样的边界条件,其中一个是LumpedRLC,指的是集中元RLC参数,而电容其实就是一个集中元器件,所以可以用这个边界进行仿真,方法:先按照电容的实际摆放位置使用HFSS里面的box命令画4个焊盘(差分AC耦合两个电容),然后应用rect命令分别画一个矩形,该矩形大小应该小于等于这2个焊盘的实际大小(电容不能大于焊盘吧),和焊盘的上表面重合,一定要重合,不然相当于电容没有放在焊盘上面;然后设置边界条件,选择Lumped RLC,在里面会有电容大小的设置,这样就ok,就可以进行其他设置仿真了

电容的4个焊盘

加上2个Lumped RLC边界,构成电容。

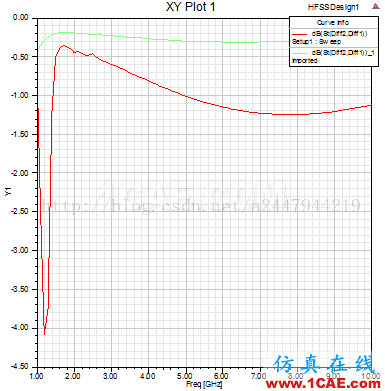

下面上一下仿真结果:

上图中分别是地层挖空和不挖空的插损参数,绿色的是地层挖空,挖空大小和4个焊盘所占的大小相同。

从上面仿真图可以看出地层挖空之后,信号质量能有非常大的提升。

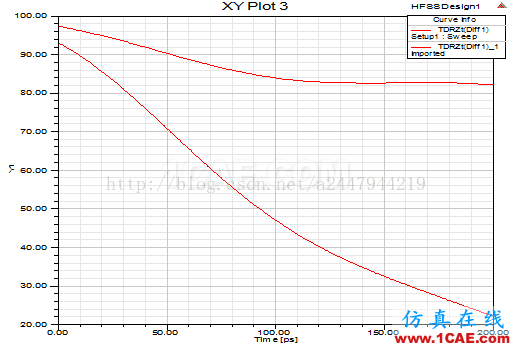

我们在看一下阻抗的变化:

地层挖空优化之后,阻抗得到了极大的改善。

其实还可以通过参数扫描,找出最合适的地层挖空大小,在这里就不贴出来仿真结果了。

相关标签搜索:高速数字电路AC耦合电容HFSS仿真 HFSS电磁分析培训 HFSS培训课程 HFSS技术教程 HFSS无线电仿真 HFSS电磁场仿真 HFSS学习 HFSS视频教程 天线基础知识 HFSS代做 天线代做 Fluent、CFX流体分析 HFSS电磁分析