# 信号完整性基础知识

张士贤编写

中兴通讯上海第一研究所

# 前 言

近年来,通讯技术、计算机技术的发展越来越快,高速数字电路在设计中的运用越来越多,数字接入设备的交换能力已从百兆、千兆发展到几十千兆。高速数字电路设计对信号完整性技术的需求越来越迫切。

在中、大规模电子系统的设计中,系统地综合运用信号完整性技术可以带来很多好处, 如缩短研发周期、降低产品成本、降低研发成本、提高产品性能、提高产品可靠性。

数字电路在具有逻辑电路功能的同时,也具有丰富的模拟特性,电路设计工程师需要通过精确测定、或估算各种噪声的幅度及其时域变化,将电路抗干扰能力精确分配给各种噪声,经过精心设计和权衡,控制总噪声不超过电路的抗干扰能力,保证产品性能的可靠实现。

为了满足中兴上研一所的科研需要,我们在去年和今年关于信号完整性技术合作的基础上,克服时间紧、任务重的困难,编写了这份硬件设计培训系列教材的"信号完整性"部分。由于我们的经验和知识所限,这部分教材肯定有不完善之处,欢迎广大读者和专家批评指正。

本教材的对象是所内硬件设计工程师,针对我所的实际情况,选编了第一章——导论、第二章——数字电路工作原理、第三章——传输线理论、第四章——直流供电系统设计,相信会给大家带来益处。同时,也希望通过我们的不懈努力能消除大家在信号完整性方面的烦脑。

在编写本教材的过程中,得到了沙国海、张亚东、沈煜、何广敏、钟建兔、刘辉、曹俊等的指导和帮助,尤其在审稿时提出了很多建设性的意见,在此一并致谢!

张士贤 2000年10月31日

### 术语、符号和缩略语

术语

### 1. 信号完整性(Signal Integrity)

信号完整性是指信号在信号线上的质量。信号具有良好的信号完整性是指当在需要的时候具有所必需达到的电压电平数值。

#### 2. 传输线 (Transmission Line)

传输线是一个网络(导线),并且它的电流返回到地或电源。

#### 3. 特性阻抗 (Characteristic Impedance)

组成信号传输回路的两个导体之间存在分布电感和分布电容,当信号沿该导体传输时,信号的跃变电压(V)和跃变电流(I)的比值称为特性阻抗( $Z_0$ ),即  $Z_0=V/I$ 。

#### 4. 反射 (Reflection)

反射就是在传输线上的回波。信号功率(电压和电流)的一部分传输到线上并达到负载处,但是有一部分被反射了。如果源端与负载端具有相同的阻抗,反射就不会发生。

### 5. 串扰 (Crosstalk)

串扰是两条信号线之间的耦合。信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。

#### 6. 讨冲 (Overshoot)

过冲就是第一个峰值或谷值超过设定电压。对于上升沿是指最高电压,而对于下降沿是指最低电压。过分的过冲能够引起保护二极管工作,导致过早地失效。

#### 7. 下冲 (Undershoot)

下冲是指下一个谷值或峰值。过分的下冲能够引起假的时钟或数据错误(误操作)。

#### 8. 电路延迟

指信号在器件内传输所需的时间(Tnd)。例如,TTL的电路延迟在3~20nS 范围。

#### 9. 边沿时间

器件输出状态从逻辑低电平跃变到高电平所需要的时间(信号波形的 10~90%),通常表示为上升沿( $T_r$ )。器件输出状态从逻辑高电平下降到低电平所需要的时间(信号波形的 90~10%),通常表示为下降沿( $T_f$ )。

#### 10. 占空比偏斜

信号传输过程中,从低电平到高电平的转换时间与从高电平到低电平的转换时间之间的差别,称为占空比偏斜。TTL和CMOS信号的占空比偏斜问题较为突出,主要是因为其输出的上升沿和下降沿延迟不同。

### 11. 输出到输出偏斜

同一器件不同输出引脚之间的信号延迟差别,称为输出到输出偏斜。

#### 12. 器件到器件偏斜

由于制造工艺和使用环境的变化,造成的不同器件对应引脚之间的信号延迟差别,称为器件到器件偏斜。通常,器件之间的偏差远大于其他类型的偏斜。

#### 13. 动态偏斜

主要是指由于温度变化、地或电源噪声造成阀值电平随时间漂移,从而产生信号延迟的变化。

2

# 符号和缩略语

VOH

—

输出高电平

VOL

—

输出低电平

VIH

—

输入高电平

VIL

—

输入低电平

VT

—

阀值电平

VOHMIN

输出高电平最小值

VOLMAX

输出低电平最大值

VIHMIN

输入高电平最小值

VILMAX

输入低电平最大值

IOL

输出低电平电流

I<sub>OH</sub> — 输出高电平电流

3

# 目录

| 第1 | 章 高速       | 医数字系统设计的信号完整性分析导论                | 7  |

|----|------------|----------------------------------|----|

| 1  | . 1.基本     | 概念                               | 7  |

| 1  | . 2. 理想    | 引的数字信号波形                         | 7  |

|    | 理想的        | TTL 数字信号波形                       | 7  |

|    | 1. 2. 2.   | 理想的 CMOS 数字信号波形                  | 7  |

|    | 1. 2. 3.   | 理想的 ECL 数字信号波形                   | 8  |

| 1  | . 3. 数字    | ·<br>经信号的畸变(或信号不完整)              | 8  |

|    | 1. 3. 1.   | 地线电阻的电压降的影响——地电平(0 电平)直流引起的低电平提高 | 8  |

|    | 1. 3. 2.   | 信号线电阻的电压降的影响                     | 8  |

|    | 1. 3. 3.   | 电源线电阻的电压降的影响                     | 10 |

|    | 1. 3. 4.   | 转换噪声                             | 11 |

|    | 串扰噪        | 声                                | 11 |

|    | 1. 3. 6.   | 反射噪声                             | 12 |

|    | 1. 3. 7.   | 边沿畸变                             | 12 |

| 1  | . 4. 研究    | 飞的目的                             | 13 |

|    | 1. 4. 1.   | 降低产品成本(略)                        | 13 |

|    | 1. 4. 2.   | 缩短研发周期,降低开发成本(略)                 | 13 |

|    | 1. 4. 3.   | 提高产品性能(略)                        | 13 |

|    | 1. 4. 4.   | 提高产品可靠性                          | 13 |

| 1  | . 5. 研乡    | 飞领域                              | 14 |

|    | 1. 5. 1.   | 各种电路工作原理(略)                      | 14 |

|    | 1. 5. 2.   | 各种电路噪声容限(略)                      | 14 |

|    | 1. 5. 3.   | 各种电路在系统中的噪声(略)                   | 14 |

|    | 1. 5. 4.   | 系统各部件的频率特性(略)                    | 14 |

|    | 1. 5. 5.   | 信号传输(略)                          | 14 |

|    | 1. 5. 6.   | 信号延迟(略)                          | 14 |

|    | 1. 5. 7.   | PCB 结构设计 (略)                     | 14 |

|    | 1. 5. 8.   | 电源分配设计(略)                        | 14 |

|    | 1. 5. 9.   | 地、电源滤波(略)                        | 14 |

|    | 1. 5. 10   | ). 热设计(略)                        | 14 |

| 1  | . 6. 研学    | 【手段                              | 14 |

|    | 1. 6. 1.   | 物理实验验证(略)                        | 14 |

|    | 1. 6. 2.   | 数学模型计算(略)                        | 14 |

|    | 1. 6. 3.   | 软件模拟分析(略)                        | 14 |

|    | 1. 6. 4.   | 经验规则估计                           | 14 |

| 第2 | 章 数字       | <sup>2</sup> 电路工作原理              | 15 |

| 2  | . 1. 数字    | 子电路分类                            | 15 |

|    | 2. 1. 1.   | GaAs(砷化钾)速度快,但功耗大,制作原料剧毒,未成熟使用;  | 15 |

|    | 2. 1. 2.   | 硅: 使用极为广泛,处于不断发展中;               | 15 |

| 2  | . 2. 基本    | 站构和特点                            | 17 |

|    | <i>TTL</i> |                                  | 17 |

|   | 2.2.2. CMOS 速度接近于 TTL,功耗小,单元尺寸小,适合于大规模集成 | 17 |

|---|------------------------------------------|----|

|   | 2.2.3. LVDS: 低电压数字系统                     | 17 |

|   | 2. 2. 4. ECL (PECL)                      | 18 |

|   | 2.3. 电路特性                                | 19 |

|   | 2.3.1. 转换特性                              | 19 |

|   | 2.3.2. V/I 特性: 电压与电流之间的关系特性曲线            | 20 |

|   | 2.3.3. 热特性及寿命                            | 23 |

|   | 2.3.4. 直流噪声容限 N <sub>MDC</sub>           | 24 |

|   | 2.3.5. 交流噪声容限 NMAC                       | 24 |

|   | 2.4. 电路互连                                | 25 |

|   | 2.4.1. 工作电压:器件工作时,施加于器件电源脚上的电压           | 25 |

|   | 2.4.2. 逻辑电平范围                            | 25 |

|   | 2.4.3. 噪声 (N)                            | 25 |

|   | 2.5. 电路选型基本原则                            | 27 |

|   | 2.5.1. 采用标准器件                            |    |

|   | 2.5.2. 够用原则,不追求高性能                       | 27 |

|   | 2.5.3. 尽可以减少品种和类型。                       | 27 |

| 第 | 3 章 传输线理论                                | 28 |

|   |                                          |    |

|   | 3.1. 基本概念                                |    |

|   | 3. 2. 传输线基本特性:                           |    |

|   | 3.2.1. 传输线特性阻抗                           |    |

|   | 3.2.2. 传输线的时间延迟                          |    |

|   | 3. 3. 传输线的分类                             |    |

|   | 3.3.2. 平衡式传输线                            |    |

|   | 3.4. 常用传输线                               |    |

|   | 3. 4. 1. 圆导线                             |    |

|   | 3.4.2. 微带线                               |    |

|   | 3.4.3. 带状线                               |    |

|   | 3.5. 反射和匹配                               |    |

|   | 3. 5. 1. 反射系数                            |    |

|   | 3.5.2. 反射的计算:                            |    |

|   | 3.5.3. 传输线的临界长度                          |    |

|   | 3.5.4. 终端的匹配和端接                          |    |

|   | 3.6. 串扰: 串扰模型图如下                         |    |

|   | 3.7. 负载效应                                |    |

|   | 3.7.1. 直流负载和交流负载                         |    |

|   | 3. 7. 2. 最小间隔                            |    |

|   | 3.7.3. 集中负载                              |    |

|   | 3.7.4. 分布负载                              |    |

|   | <b>经</b> 向负载                             |    |

|   | 7.8. 负载驱动方式                              |    |

|   | 3.8.1. 点对点                               |    |

|   | 事推                                       |    |

|   |                                          |    |

# 信号完整性基础知识

| 3. 8. 3. | 星型                     | . 46 |

|----------|------------------------|------|

| 扇型       |                        | . 46 |

| 3.9. 传输  | 线损耗和信号质量               | 46   |

| 3. 9. 1. | 集肤效应                   | . 46 |

| 3. 9. 2. | 邻近效应                   | . 46 |

| 3. 9. 3. | 辐射损耗                   | . 47 |

| 3. 9. 4. | 介质损耗                   | . 47 |

| 第4章 直流   | 〔电源分布系统设计              | . 48 |

| 4.1. 基本  | 概念                     | 48   |

| 4. 1. 1. | 电源分布系统                 | . 48 |

| 4. 1. 2. | 平面                     | . 48 |

| 4. 1. 3. | 平面(Plane)为电流回路提供最低阻抗回路 | . 48 |

| 4.2. 设计  | ·目标                    | 48   |

| 4. 2. 1. | 为数字信号提供稳定的电压参考;        | . 48 |

| 4. 2. 2. | 为逻辑电路提供低阻抗的接地连接;       | . 48 |

| 4. 2. 3. | 为逻辑电路提供低阻抗的电源连接;       | . 48 |

| 4. 2. 4. | 为电源和地提供低交流阻抗的通路;       | . 48 |

| 4. 2. 5. | 为数字逻辑电路工作提供电源          | . 49 |

| 4.3. 一般  | 设计规则                   | 50   |

| 4.4. 多层  | 板的叠层结构                 | 50   |

| 4.4.1.   | 叠层结构的设计主要考虑以下因素        | . 50 |

| 4. 4. 2. | 在高速数字设计中的一般规则是         | . 51 |

| 4.5. 电流  | 回路                     | 52   |

| 4. 5. 1. | 基本概念                   | . 52 |

| 4. 5. 2. | 环路面积                   | . 52 |

| 4. 5. 3. | 参考平面的开槽                | . 53 |

| 4. 5. 4. | 连接器的隔离盘                | . 53 |

| 4.6. 去耦  | 电容极其应用                 | 54   |

| 4. 6. 1. | 去耦电容                   | . 54 |

| 4. 6. 2. | 低频大容量去耦电容(BULK)        | . 55 |

| 4. 6. 3. | 高频去耦电容                 | . 56 |

| 4.6.4.   | 多层片式陶瓷电容的材料选择          | . 58 |

| 4. 6. 5. | 表面贴装电容的布局和布线           | . 58 |

| 4. 6. 6. | 多层印制板中的平面电容            | . 59 |

| 4. 6. 7. | 埋入式电容                  | . 59 |

| 4.7. 噪声  | 抑制                     | 61   |

| 4. 7. 1. | 系统电源变化                 | . 61 |

| 4. 7. 2. | 系统电源的电位差               | . 61 |

| 4. 7. 3. | 系统逻辑地的电位差              | . 61 |

| 4. 7. 4. | 地电平抖动                  | . 61 |

# 第1章 高速数字系统设计的信号完整性分析导论

# 1.1. 基本概念

高速数字设计(High-Speed Digital Design)强调被动元件的特性及其对电路性能的影响, 包括导线、印制电路板以及集成电路封装等等;

高速数字设计研究被动元件如何影响信号传输 (振铃和反射), 信号之间的相互作用 (串扰):

信号完整性 (Signal Integrity,以下简称 SI) 是指信号在信号线上的质量。 信号具有良好的信号完整性是指当在需要的时候具有所必需达到的电压电平数值;

信号完整性是保证系统稳定的基础,分析讨论系统信号完整性是非常必要的。

# 1.2. 理想的数字信号波形

无论是哪一种数字集成电路,理想的数字信号是指器件厂家提供的输出高电平(VOH)、低电平(VOL)、上升沿(tr)和下降沿(tf)等参数所描述的信号波形。

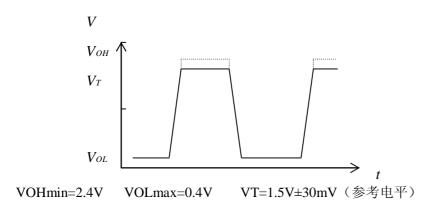

# 1.2.1. 理想的 TTL 数字信号波形

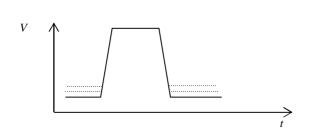

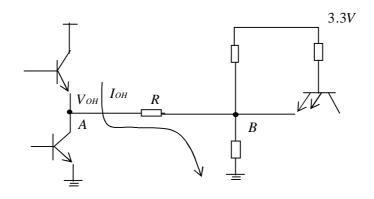

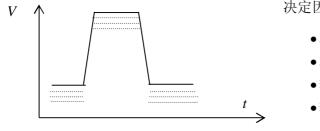

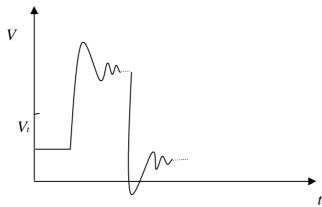

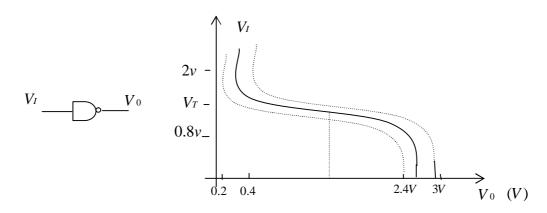

下图所示为理想的 TTL(含 LVTTL)数字信号波形

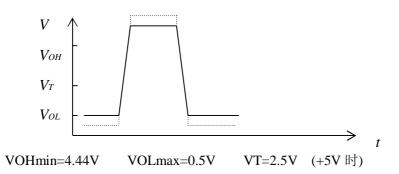

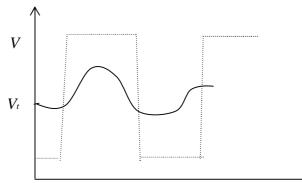

### 1.2.2. 理想的 CMOS 数字信号波形

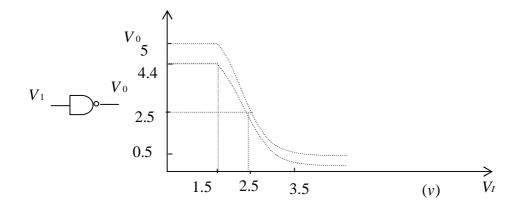

下图所示为理想的 CMOS 数字信号波形

VOHmin=2.4V VOLmax=0.4V VT=1.5V (+3.3V 时)

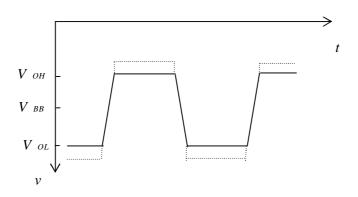

### 1.2.3. 理想的 ECL 数字信号波形

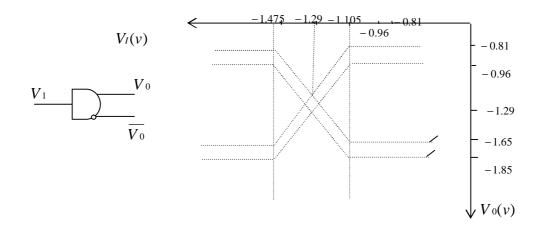

下图所示为理想的 ECL 数字信号波形

VOHmin=-0.96V VOLmax=-1.65V VBB=-1.29V±30mV(参考电平)

IC 在系统应用中不可能达到理想的程度, 由于受到多种因素的影响,信号波形会产生各种变化, 但是这些变化的程度必须严格加以限制, 使之达到可以接受的程度。主要有哪些方面的设计上的问题会造成影响或者变化,,又有多大的变化,它们之间有什么关系等都是值得讨论分析的。

# 1.3. 数字信号的畸变(或信号不完整)

本节只讨论 TTL 信号发生的畸变,是因为从目前使用的情况来看, CMOS 电路的输入、输出等外部接口电路已和 TTL 兼容,而 ECL 电路用得很少, 这里不加以讨论。 还有一些其他数字电路, 如 LVDS、GTL、NMOS、PMOS 等, 本节也不加以讨论

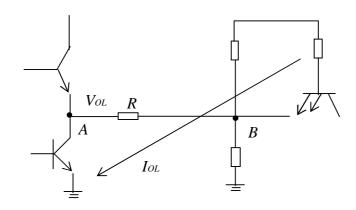

1.3.1. 地线电阻的电压降的影响——地电平(0 电平)直流引起的低电平提高见下图,图中虚线为提高的情况。提高幅度与 IC 的功耗大小、IC 密度、馈电方式、

地线电阻(R) 、馈电的地线总电流有关。  $\Delta V$  地=  $\Delta I \times \Delta R$

### 1.3.2. 信号线电阻的电压降的影响

a) IC 输出管脚经过印制导线或电缆到另一 IC 的输入脚,

输出低电平电流在印制导线或电缆电阻上引起一个低电平的抬高,其值为 ΔVOL=IOL×R。 见图中的上面一条虚线。

8

### 决定因素

- 端接方式

- 端接电平

- 端接电阻大小

- 线密

- 线厚

- 线长

• 线截面积

显而易见,低电平的抬高与印制导线电阻值及输出低电平电流有关,如下图所示:

# B点的低电平比A点的低电平高

注意:当 IC 输出脚为低电平时,如果此器件不是驱动器, 而是一般器件,则由于输出 低电平电流太大, 远大于器件手册给出的值,输出三极管将退出饱和区,进入工作区,

使输出低电平抬高很多。如下图中上面一条虚线所示:

决定因素:端接方式

端接电阻大小

输出管饱和深度

输出管β值

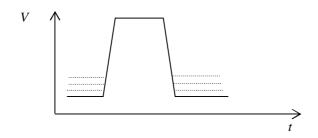

b) IC 输出管脚经过印制导线或电缆到另一个 IC 的输入脚,输出高电平电流在印制导线或电缆电阻上引起一个高电平的降低,其值为 ΔV<sub>OH</sub>=I<sub>OH</sub>× R,见下图中高电平上的下面虚线:

IOH 由下列因素决定:端接方式、端接电平、端接电阻大小

R由下列因素决定:线宽、线厚、线长

显而易见,高电平的降低与印制导线或电缆电阻值及输出高电平电流有关,如下图所 示:

B 点的高电平比 A 点的高电平要低

注意: IC 输出脚为高电平时, 如果此器件不是驱动器, 而是一般器件, 则由于输 出高电平电流太大,远大于器件手册给出的值时,输出管也会退出饱和区,进入工作区, 使输出高电平降低很多。如下图中下面一条虚线所示:

# 决定因素

- •端接方式

- •端接电阻大小

- •输出管的饱和深度

- •输出管的**b**值

### 1.3.3. 电源线电阻的电压降的影响

IC 的电源电压(如+3.3V), 如果系统中存在差值, 当小于+3.3V 时, 输出高电平将产

生一个下降值, 如上图中高电平上的虚线所示:

由于系统电源有集中电源和分散的电源模块之分,此差值不同,由于 IC 功耗的大小、IC 密度、馈电方式、电源线的馈电电阻值以及电源电流值,引起一个  $\Delta VCC$  ( $\Delta VCC$  = $\Delta I \times \Delta R$ )

以上原因,使 TTL 信号波形变得离理想波形很远了。 低电平大为提高了,高电平也大为降低了。 对这些值若不严加控制, 对系统工作的稳定可靠工作是不利的。此外,结温差,即不同功耗的器件的 P-N 结的温度不同,还会影响高低电平及门槛电平的变化也会影响系统工作。

除上面所说的直流成分之外,更为重要的是系统是以极高频率在工作,也就是说,系统内的器件、导线有各种频率的,各种转换速率的信号在动作、传递。首先是相互之间的信号电磁藕合(串扰)和信号在不同特性阻抗传输路径上的反射,以及电源,地电平由于IC高频转换引起电流尖峰电平,使TTL信号波形变得更坏。

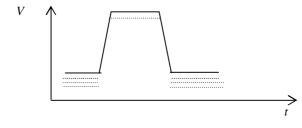

### 1.3.4. 转换噪声

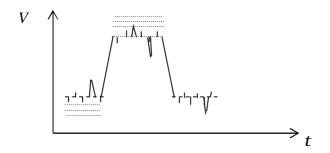

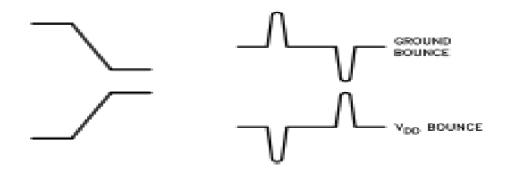

由于系统工作时, 器件以高频转换, 造成供电系统上有高频率变化的电流尖峰, 而供电的电源线路和地线路都可看成是很小的电阻、电感、电容元件。电流尖峰值太大, 在它们上面会产生较大的交流尖峰电压, 其电源上的尖峰电压基本上会串扰到高电平上, 而地电平上的尖峰电压会串扰到低电平上, 如下图所示: IC 内部同样存在这种尖峰电压。

### 决定因素

- IC集成度

- IC同时同相翻转器的个数

- IC密度

- 地电源线结构层数

- •滤波电容的性能密度

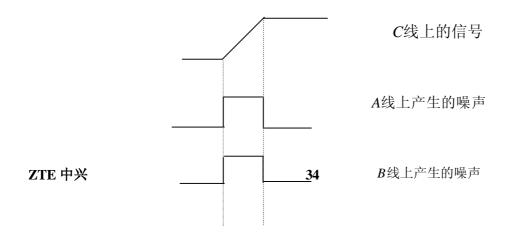

# 1.3.5. 串扰噪声

由于系统组装越来越密, 印制导线之间的距离越来越近,邻近导线上有高速转换的 电平信号。 如正跳变信号跳变的时间 tr 和负跳变的时间 tf 都很小,使得导线上已有信号 上叠加一个较大的电磁藕合信号(串扰信号)。如下图中较大的尖峰信号。这些信号还包括 插头座上的信号针之间的串扰信号以及电缆中信号之间的串扰。

决定因素: tr 与 tf 值、线宽、线间距、(基材)介质的厚度、介质的介电常数、平行线长、重叠线长、插头座信号针地针比、电缆信号线地线比。

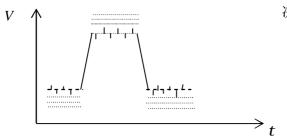

# 1.3.6. 反射噪声

如果 IC 之间的互连线比较长 (复杂系统往往是这样) ,线的特性阻抗 又不均匀,或者终端没有匹配,会引起反射,如果始端也不匹配,则会来回 反射而造成振铃。如下图所示:

决定因素:特性阻抗、匹配方式、失配大小

终端反射系数、始端反射系数、线长

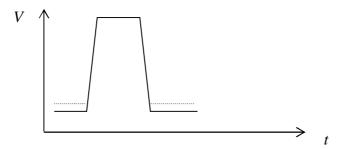

# 1.3.7. 边沿畸变

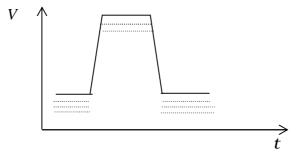

如果信号频率升高到一定程度,也就是器件工作频率达到一定的高度极限,而且印制导线又较长或者负载电容较大时, tr ≥tw 上升时间等于或大于脉冲宽度,信号畸变到没有高低电平平顶或者远离平顶。如下图所示(实线):

举例"仿真或示波器实测"均可验证。

决定因素:线宽、线长、基材介质厚度、介质介电常数、负载数、工作频率(脉宽)、tr 数字信号的变化。讨论了上面七条,可见其畸变不容忽视。如果任其自流,不严加限制,造出来的系统不可能稳定、可靠的工作。

# 1.4. 研究的目的

在中、大规模电子系统的设计中,系统地运用信号完整性技术可以带来许多益处

- 1.4.1. 降低产品成本(略)

- 1.4.2. 缩短研发周期,降低开发成本(略)

- 1.4.3. 提高产品性能(略)

# 1.4.4. 提高产品可靠性

数字电路在具有逻辑功能的同时,也具有丰富的模拟特性。

数字电路本身具有一定的抗干扰能力,设计工程师可以估计或精确测定各种噪声的幅度及其时域变化,将电路抗干扰能力精确分配给各种噪声,控制总噪声不超过电路的抗干扰能力,以最小的综合成本达到最高的整体性能。

- 1.5. 研究领域

- 1.5.1. 各种电路工作原理(略)

- 1.5.2. 各种电路噪声容限(略)

- 1.5.3. 各种电路在系统中的噪声(略)

- 1.5.4. 系统各部件的频率特性(略)

- 1.5.5. 信号传输(略)

- 1.5.6. 信号延迟(略)

- 1.5.7. PCB 结构设计(略)

- 1.5.8. 电源分配设计(略)

- 1.5.9. 地、电源滤波(略)

- 1.5.10. 热设计(略)

- 1.6. 研究手段

- 1.6.1. 物理实验验证(略)

- 1.6.2. 数学模型计算(略)

- 1.6.3. 软件模拟分析(略)

- 1.6.4. 经验规则估计

通常需要综合运用上述四种方法。

# 第2章 数字电路工作原理

- 2.1. 数字电路分类

- 2.1.1. GaAs(砷化钾)速度快,但功耗大,制作原料剧毒,未成熟使用;

- 2.1.2. 硅: 使用极为广泛,处于不断发展中;

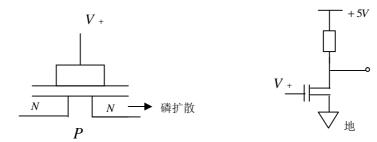

- 2.1.2.1. 单极型: 一个元件的电极上只有一种扩散类型,或者说只有一种半导体类型 (N) 或 (N) 或 (N) ;

- 2.1.2.1.1. PMOS: P型金属物半导体

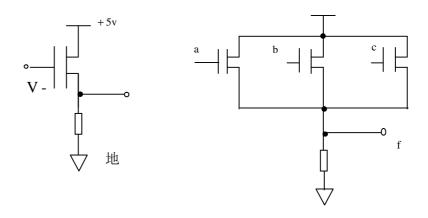

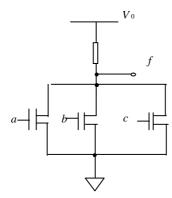

$$f = \overline{a \cdot b \cdot c}$$

### 2.1.2.1.2. NMOS:N 型金属氧化物半导体

$$f = \overline{a + b + c}$$

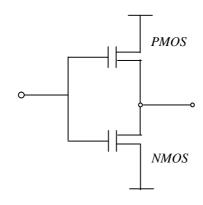

### 2.1.2.1.3. CMOS 互补型金属氧化物半导体

工作在直流为 0 (只有漏电流  $0.5 \,\mu$  A 左右),所以功耗只有原来几千分之一,速度快、结构简单,适合大规模集成(功耗因素、尺寸因素、工艺因素)

- 2.1.2.2. 双极型: 一个元件的电极上有两种扩散类型,或者说有两种半导体类型(N 或 P)

- 2.1.2.2.1. TTL:速度快、功耗低,但输出管工作在饱和区,存储时间较长。 (STTL、LSTTL、ALSTTL、ASTTL、FTTL、LVTTL) 以上为不断改进的器件类型。

- 2.1.2.2.2. ECL 高速度、高功耗、电流藕合型,电压摆幅小。 (ECL<sub>1.II.III</sub>、ECL<sub>10K</sub>、ECL<sub>10K</sub>、ECL<sub>10H</sub>、ECL<sub>10E</sub>、ECL<sub>10E</sub>)改进型。

# 2.2. 基本结构和特点

# 2.2.1. TTL

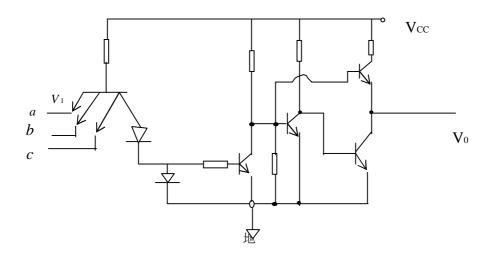

$\overline{V_0} = a \cdot b \cdot c$

结构如图示,速度快、功耗低于 ECL。工作电平:

$egin{array}{lll} V_{OHMIN}\!\!=\!\!2.4V & V_{OLMAX}\!\!=\!\!0.4V \\ V_{IHMIN}\!\!=\!\!2V & V_{ILMAX}\!\!=\!\!0.8V & V_{T}\!\!=\!\!1.5V \\ \end{array}$

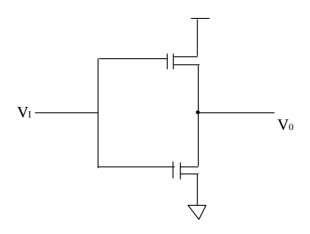

# 2.2.2. CMOS 速度接近于 TTL, 功耗小, 单元尺寸小, 适合于大规模集成

工作电平:  $V_{Ohmin}$ =4.44V  $V_{OLMAX}$ =0.5V  $V_{IHMIN}$ =3.5V  $V_{ILMAX}$ =1.5V  $V_{T}$ =2.5V

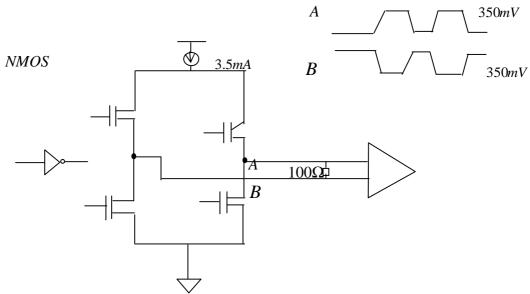

# 2.2.3. LVDS: 低电压数字系统

功耗小(驱动器功耗 1.2 mW)摆幅小(350 mV)速度快,不慢于 ECL,由于恒流源特性,抗干扰能力特别强,差动传输可减少传输线数量,压缩( $18 \rightarrow 21$ ) $\rightarrow 4$  对;

# 2. 2. 4. ECL (PECL)

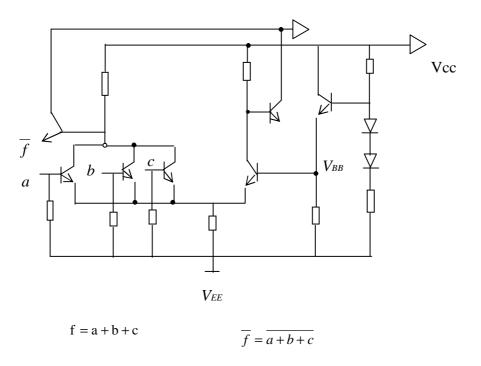

电路结构如下图:

$V_{OHmin}$ =-0.96V  $V_{OLmax}$ =-1.65V

$V_{IHmin}$ =-1.105V  $V_{ILmax}$ =-1.475V  $V_{BB}$ =-1.29V

PECL(伪 ECL), $V_{EE}$ 抬高到  $V_{CC}$ , $V_{CC}$ 抬高到正电压,达到与 TTL 共电源工作。此时各工作电平同时抬高一个  $V_{CC}$ 值,如  $V_{OHMIN}$ =-0.96V+  $V_{CC}$

# 2.3. 电路特性

### 2.3.1. 转换特性

转换特性是指输出电平随输入电平变化的特性曲线。

### 2.3.1.1. TTL 电路的转换特性

TTL 电路的转换特性曲线如上图,两条虚线之间的区域为器件的工作区。从曲线可看出其最坏情况就是边界点即  $V_{OH}$  时为 2.4v, $V_{OL}$  时为 0.4v, $V_{IH}$  时为 2v, $V_{IL}$  时为 0.8v,这四个值非常重要,因为输出的边界值与输入的边界值之差(同极性时)为安全区即直流抗干扰能力(NM)

### 2.3.1.2. CMOS 的转换特性: 曲线如下图:

两条曲线之间的区域为器件工作区,分析它的方法同上面的 TTL。可以看出,它与 TTL 的曲线差别很大,所以在与 TTL 互连时,应加以考虑,目前随着工艺的不断改进,使 CMOS 的工作区接近 TTL,或者器件外围电路直接用 TTL 的电路,达到完全互连兼容。

19

# 2.3.1.3. LVDS 的转换特性

略

# 2.3.1.4. ECL 的转换特性:

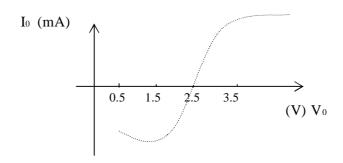

曲线如下图:

$V_{O}$ 及  $V_{O}$  的两条虚线之间区域为 ECL 的工作区, $V_{O}$  的最坏边界与  $V_{I}$  的最坏边界之差为 直流电平抗干扰能力(NM)

# 2.3.2. V/I 特性:电压与电流之间的关系特性曲线

# 2.3.2.1. 输入 V/I 特性

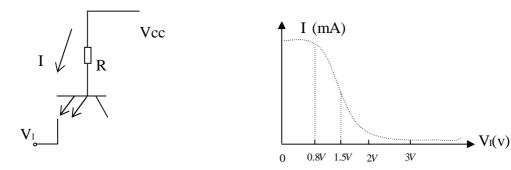

输入电压与输入电流之间的特性曲线

# 2.3.2.1.1. TTL 电路的 V/I 输入特性

上图为 TTL 的 V/I 输入特性

电流最大值为(Vcc-0.8v)/R, 电流最小值为漏电流(0.05 μ A 左右)

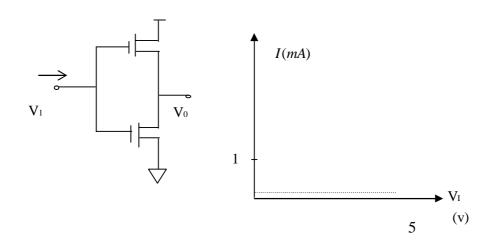

### 2.3.2.1.2. CMOS 电路的 V/I 输入特性:

上图为 CMOS 电路的 V/I 输入特性, $V_1$  输入电压从低到高变化情况下,输入电流都为 0 (漏电流)

### 2.3.2.1.3. LVDS 电路的 V/I 输入特性同 CMOS

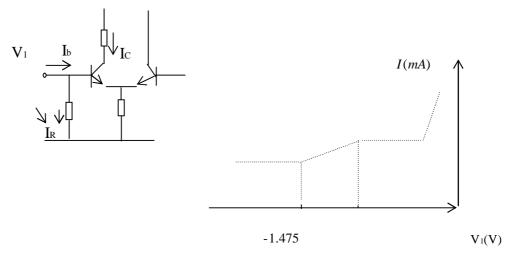

### 2.3.2.1.4. ECL 电路的输入 V/I 特性,如下图示:

$V_1$  大于-1.105V 小于-0.4V 时, $I=I_b+I_R$  、 $I_{b=}=I_C/\beta$   $I_R=V_1/R$   $V_1$  小于-1.475V 时  $I=I_R$  , $V_1$  大于-0.04v 时, $I_B$  为饱和电流,此时  $V_1$  抬高时,输入电流 I 急骤增加。

# 2.3.2.2. 输出 $V_0/I_0$ 特性:器件的输出电压与输出电流之间的关系曲线

# 2.3.2.2.1. TTL 输出 $V_O/I_0$ 特性,如图示:

此曲线为输出推长线且并联匹配时的  $V_O/I_0$  特性曲线,其值可由端接电阻值计算出输出电流  $I_o$

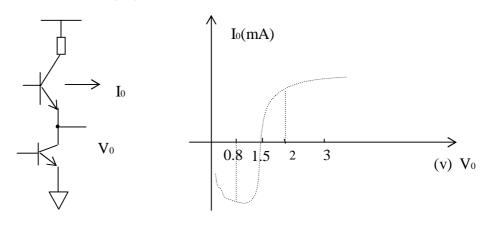

# 2.3.2.2.2. CMOS 输出 V<sub>O</sub>/I<sub>0</sub> 特性

见下图,图中不端接时的  $V_0/I_0$  特性,

如果端接时, $V_O/I_0$  特性如下图:

# 2.3.2.2.3. LVDS 输出 V<sub>O</sub>/I<sub>0</sub> 特性

略

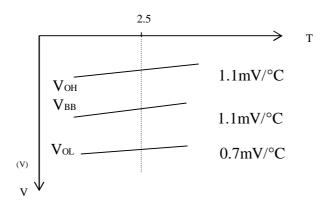

2.3.2.2.4. ECL 输出 V<sub>0</sub>/ I<sub>0</sub> 特性, 如下图:

Vo

Vo

Vo (V) -1.475 -1.29 1.105

输出电流  $I_O = V_O/R$ ,R 为并联端接电阻值。

# 2.3.3. 热特性及寿命

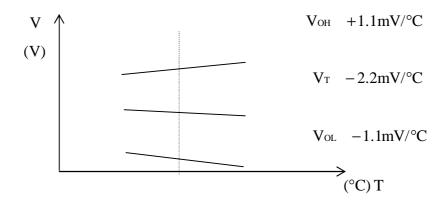

2. 3. 3. 1. TTL 电路的热特性见下面曲线,不同结温的器件互连,低电平造成  $1.1 \text{mV}/\mathbb{C}$  的噪声,高电平造成  $3.3 \text{mV}/\mathbb{C}$  的噪声

# 2.3.3.2. CMOS 热特性

略

# 2.3.3.3. LVDS 热特性

略

# 2.3.3.4. ECL 热特性

曲线如图,不同结温的器件互连 高低电平造成约 1.1mV/℃的噪声

温升会对寿命加速

分析略

# 2.3.4. 直流噪声容限 N<sub>MDC</sub>

### 2.3.4.1. 高电平直流噪声容限 N<sub>HMDC</sub>

### 2.3.4.1.1. TTL 高电平直流噪声容限 N<sub>HMDC</sub>

$N_{HMDC} = V_{OHMIN} - V_{IHMIN} = 2.4V - 2V = 0.4v = 400mV$

### 2.3.4.1.2. CMOS 高电平直流噪声容限 NHMDC

$N_{HMDC} = V_{OHMIN} - V_{IHMIN} = 4.44V - 3.5V = 0.906V = 906mV$

# 2.3.4.1.3. LVDS 高电平直流噪声容限 略

### 2.3.4.1.4. ECL 高电平直流噪声容限 NHMDC

$N_{HMDC} = V_{OHMIN} - V_{IHMIN} = -0.96V - (-1.105V) = 0.145V = 145mV$

#### 2.3.4.2. 低电平直流噪声容限 NLMDC

### 2.3.4.2.1. TTL 低电平直流噪声容限 NLMDC

$N_{LMDC} = V_{ILMAX} - V_{OLMAX} = 0.8v - 0.4v = 0.4v = 400 \text{mV}$

### 2.3.4.2.2. CMOS 低电平直流噪声容限 NLMDC

$N_{LMDC} = V_{ILMAX} - V_{OLMAX} = 1.5v - 0.5v = 1v = 1000mV$

# 2.3.4.2.3. LVDS 低电平直流噪声容限 NLMDC 略

### 2.3.4.2.4. ECL 低电平直流噪声容限 NLMDC

$N_{LMDC} = V_{ILMAX} - V_{OLMAX} = -1.475v - (-1.65v) = 0.175v = 175mV$

### 2.3.5. 交流噪声容限 NMAC

#### 2.3.5.1. 高电平交流噪声容限 NHMAC

### 2.3.5.1.1. TTL 高电平交流噪声容限 NHMAC

$N_{HMAC} = V_{IHMIN} \cdot (V_{T} + 30mV) = 2v-1.53v = 0.47v = 470mV$

其中 30mV 为  $V_{\text{T}}$  离散  $\pm 30\text{mV}$ ,以下同。

### 2.3.5.1.2. CMOS 高电平交流噪声容限 NHMAC

$N_{HMAC} = V_{IHMIN} - (V_T + 30mV) = 3.5V - (2.5V + 30mV) = 0.97V = 970mV$

# 2. 3. 5. 1. 3. LVDS 高电平交流噪声容限 NHMAC 略

### 2.3.5.1.4. ECL 高电平交流噪声容限 NHMAC

$N_{HMAC} = V_{IHMIN} - (V_{BB} + 30 \text{mV}) = -1.105 V - (-1.26 V) = 0.155 V = 155 \text{mV}$

#### 2.3.5.2. 低电平交流噪声容限 NLMAC

### 2.3.5.2.1. TTL 低电平交流噪声容限 NLMAC

$N_{MAC} = V_T - 30mV - V_{ILMAX} = 1.5V - 0.03V - 0.8V = 0.67V = 670mV$

### 2.3.5.2.2. CMOS 低电平交流噪声容限 N<sub>LMAC</sub>

$N_{LMAC} = V_T - 30mV - V_{ILMAX} = 2.5V - 30mV - 1.5V = 0.97V = 970mV$

### 2.3.5.2.3. LVDS 低电平交流噪声容限

略

### 2.3.5.2.4. ECL 低电平交流噪声容限 NLMAC

$N_{LMAC} = V_{BB} - 30 \text{mV} - V_{ILMAX} = -1.29 V - 0.03 V - (-1.475 V) = 0.155 V = 155 \text{mV}$

# 2.4. 电路互连

## 2.4.1. 工作电压: 器件工作时,施加于器件电源脚上的电压

- 2.4.1.1. TTL工作电压 +5V→地 3.3V→地

- 2.4.1.2. CMOS 工作电压 +5V→地 3.3V→地 2.5V→地 1.8V→地

- 2.4.1.3. LVDS 工作电压 3.3V→地

### 2.4.2. 逻辑电平范围

逻辑电平范围指逻辑"1"电平范围和逻辑"0"电平的范围。

#### 2.4.2.1. TTL 逻辑电平范围

逻辑"1"电平: 2V→5V

逻辑"0"电平: 0V→0.8V

#### 2.4.2.2. CMOS 逻辑电平范围

逻辑"1"电平: 3.5V→5V 2V→3.3V

逻辑"0"电平: 0V→1.5V 0V→0.8V

#### 2.4.2.3. ECL 逻辑电平范围:

逻辑"1"电平: -0.96V→-0.81V

逻辑"0"电平: -1.65V→-1.85V

### 2.4.3. 噪声(N)

本节只讨论 TTL 电路

### 2.4.3.1. 直流噪声 NDC

#### 2.4.3.1.1. 高电平直流噪声 NHDC

电源电压差引起的高电平直流噪声(电源模块分散供电时)100%呈现在高电平上,占用高电平直流噪容限。

电源馈电在器件电源脚上的差,100%呈现在高电平上,占用高电平直流噪声容限。

器件推长线时,如果采用并联端接(匹配),印制导线电阻上的压降使高电平降低,占用 直流噪声容限:

同上,由于并联端接有较大高电平输出电流,使输出管退出饱和,进入工作区,使  $V_{CE}$  压降增大,而降低  $V_{OH}$  降低值,也占用直流噪声容限

以上四项之和,不可超过400mV,也就是高电平直流噪声不可大于高电平直流噪声容限。

### 2.4.3.1.2. 低电平直流噪声 M<sub>LDC</sub>

电源馈电,流经地线(或面)电流,因存在地线电阻,引起器件地脚上存在电位差 ΔV地,100%呈现在低电平上,占用低电平直流噪声容限。

器件推长线时,如果采用并联端接(匹配),印制导线电阻上的压降使低电平抬高, 占用低电平直流噪声容限。

同上,由于并联匹配,输出低电平电流较大,使输出管退出饱和进入工作区,使  $V_{CE}$  压降增大,而抬高输出低电平  $V_{OL}$  ,抬高值也占用低电平直流噪声容限。

以上三项之和,不可大于 400mV, 也就是说,低电平直流噪声不可大于低电平直流噪声容限。

### 2.4.3.2. 交流噪声 N<sub>AC</sub>

### 2.4.3.2.1. 高电平交流噪声 NHAC

电源线上的电流尖峰引起电压尖峰噪声,此噪声基本100%藕合到输出高电平上。

由于长线转输信号时,不匹配或者失配进,正跳变信号会有过冲和反冲(反射引起)信号, 其反冲构成高电平时的交流噪声。

输出高电平上,由于邻近的平行线或者重叠线上有 dv/dt,dI/dt 通过分布电容和电感串扰 到此高电平上,产生高电平上的串扰噪声。串扰噪声还会在插头座和电缆上的相邻信号针 或线之间产生。

以上三项其值都不小,但它们是随机产生,不易发生在同一时刻,因此不是相加的关系。

### 2.4.3.2.2. 低电平交流噪声 N<sub>LAC</sub>

逻辑地线上的电流尖峰引起器件地脚上的电压尖峰,100%藕合到输出低电平上。

长线传输信号时,不匹配或者失配时,负跳变信号会有过冲和反冲,其反冲构成低电平的交流噪声。

输出低电平上,由于邻近的平行线或重叠线或者插头座上邻近的针或者电缆线上邻近的线

上有跳变信号,dv/dt,dI/dA 通过分布电容和电感串扰到此低电平上,产生低电平的串扰噪声。

以上三项也不是相加的关系。

- 2.5. 电路选型基本原则

- 2.5.1. 采用标准器件

- 2.5.2. 够用原则,不追求高性能

- 2.5.3. 尽可以减少品种和类型。

# 第3章 传输线理论

# 3.1. 基本概念

对于数字信号而言,传输线理论讨论的问题是高速谐波信号在传输导线之上的传输问题。谐波信号分为电压谐波和电流谐波,谐波信号有一个频率 (f),还有一个传输的速度问题,频率与速度反应一个波长问题,而速度又有一个延迟时间问题,它们之间的关系是讨论的重点。由于传输受阻,由阻抗引起的反射也是讨论的重点。数字信号的平顶部份,我们认为是频率为 0,不加讨论,信号的正跳变  $t_r$  和负跳变  $t_f$  (为便于讨论假定  $t_r$ = $t_f$ ) 把它们之和看作谐波的周期。

频率  $f=1/T=1/(t_r+t_f)=1/(2t_r)=0.5/t_r$

所以我们把 0.5/t<sub>r</sub>看作是数字信号的模拟频率,又称一次谐波频率,这个参数在数字电路讨论中经常要使用。

数字信号的谐波信号在一般传输线中的传输约为每米 6nS 左右, 其速度:

v=m/ (6\*10<sup>-9</sup>s) =16.66\*10<sup>7 m</sup>/s (左右)

它比波在空气中的传输速度要慢得多。

*I*——电流 *L*——线长

E——电场强度 H——磁场强度  $\Phi$ ——磁通量

根据库仑定律:  $E=Q/(4\pi \epsilon r^2)$

$V=\int E^{\bullet} d\mathbf{r}$

E——电场(伏特/米) Q——电荷(库仑)

$\varepsilon$  ——介电常数 r ——距离 (米) —半径 (离源)

导体中电流将产生磁场,表示为:

$$\int H \cdot dr = I$$

或 $dB = \frac{\mathbf{m} \cdot I \cdot dr}{4pr^2}$

$\Phi = \int B d_r$

r----半径(米)

*I*——电流(安培)

**B**——磁通密度(韦伯/米<sup>2</sup>)

H---磁场强度(安培/米)

μ ——导磁率

Φ---磁通量(韦伯)

根据法拉弟定律: V=d<sub>0</sub>/d<sub>t</sub>

$V \!\!=\!\! L \bullet (d_i \! / d_t)$

由于 VI 实际上是时间的函数, I 也是时间的函数,使得 E、H、B、 $\Phi$ 均为时间的函数,所以产生的感应电压 V 也是时间的函数。

传输线模型中实际存在四要素:

- 一个串联电阻;

- 一个串联电感;

- 一个并联电容——C=Q/V;

- 一个并联电导——导体间的介质损耗。

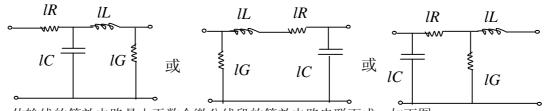

- 一个传输线的微分线段 l 可以用等效电路描述如下:

传输线的等效电路是由无数个微分线段的等效电路串联而成,如下图

# 3.2. 传输线基本特性:

传输线的基本特性是特性阻抗和信号的传输延迟。

# 3.2.1. 传输线特性阻抗

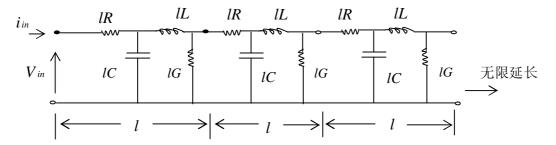

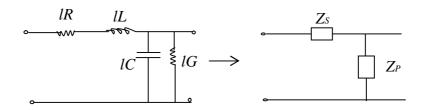

从上面讨论中,传输线的等效电路可知,每一小段线的阻抗都是相等的。传输线的特性阻抗就是微分线段的特性阻抗。

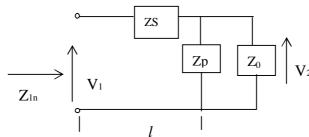

串联阻抗  $Z_{S}=1$  (R+jwL)

并联阻抗:

$$Z_P = \frac{1}{l(G+jwc)} = \frac{1}{Y_P}$$

传输线可等效为:

$$Z_{1N}=Z_1=Z_2=Z_3=Z_0$$

电路简化为

$$Z_{1N} = Z_S + \frac{Z_0 Z_P}{Z_0 + Z_P} = Z_0$$

$$\mathbb{EP} : Z_0 = \frac{Z_S + \sqrt{Z_S^2 + 4Z_S Z_P}}{2}$$

$$= \frac{l(R + jwL)}{2} + \frac{1}{2} \sqrt{l^2 (R + jwL)^2 + 4\frac{R + jwL}{G + jwc}}$$

图为 1 是微分段,极小, 1 项和 1 的平方项可忽略。

$$\therefore Z_0 = \frac{1}{2} \sqrt{4 \frac{R + jwL}{G + jwc}} = \sqrt{\frac{R + jwL}{G + jwc}} = \sqrt{Z_P Z_S}$$

$$r = \ln[1 + Z_{S}\sqrt{\frac{Y_{P}}{Z_{S}}}] = \ln(1 + \sqrt{Y_{P}Z_{S}})$$

$$\mathbf{Q}\ln(1 + A) = A - \frac{A^{2}}{2} + \frac{A^{3}}{3} - \mathbf{L}, \exists \exists \forall \overline{Y_{P}Z_{S}} \langle \langle 1 \rangle$$

$$\therefore r = \sqrt{Y_{P}Z_{S}} = l\sqrt{(R + jwl)(G + jwc)}$$

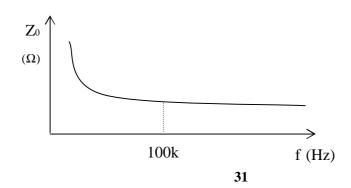

当频率足够高时(f≥100KHZ), $\omega$ =2 $\pi$ f,其值很大, $\omega$ L、 $\omega$ c 很大,R、G 可忽略,L 为单位长度线的固有电感,C 为单位长度线的固有电容,此时

$$Z_0 = \sqrt{\frac{L}{C}}$$

当频率很低时(f≤1KHZ), W=2πf很小,可以忽略

$$Z_0 = \sqrt{\frac{R}{G}}$$

$Z_0$  是传输线的特性阻抗。

特性阻抗随频率的变化曲线如下图:

**Z**<sub>0</sub>描述了传输线的特性阻抗,但是,是无损耗条件下来描述的。包括电阻上热损耗和介质 损耗都被忽略了的,也就是直流电压变化和漏电引起的电压波形畸变都未考虑在内。实际 应用中,必须具体分析。

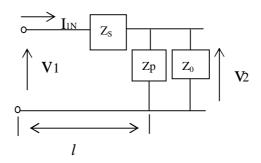

# 3.2.2. 传输线的时间延迟

一个传输线的微分线段(1)的等效电路已知如下

$$V_{2} = V_{1} \frac{Z_{P}Z_{0}}{Z_{P} + Z_{0}} \cdot \frac{1}{Z_{S} + Z_{P}Z_{0}/(Z_{P} + Z_{0})}$$

$$\overrightarrow{Z}_{S} = \frac{Z_{S}(Z_{P} + Z_{0}) + Z_{P}Z_{0}}{Z_{P}Z_{0}}$$

$$= 1 + Z_{S}(\frac{1}{Z_{P}} + \frac{1}{Z_{0}})$$

设单位长度常量

$$y = \alpha + j \beta$$

$v_2 = v_1^{-r}$

这里  $v_1^{-\alpha}$  是从  $v_1$  到  $v_2$  的信号衰减;

$v_1^{-j\beta}$ 是从  $v_1$ 到  $v_2$ 的相位变化。

$$\ln(\frac{V_1}{V_2}) = \ln e^{(a+jb)} = a + jb = r$$

$$= \ln[1 + Zs(\frac{1}{z_p} + \frac{1}{z_0})]$$

$$\therefore r = \ln\{1 + Zs[\sqrt{\frac{l(G + jwc)}{Zs}} + l(G + jwc)]\}$$

省略式中更小的项,有:

$$r = \ln[1 + Z_{S}\sqrt{\frac{Y_{P}}{Z_{S}}}] = \ln(1 + \sqrt{Y_{P}Z_{S}})$$

$$\mathbf{Q}\ln(1 + A) = A - \frac{A^{2}}{2} + \frac{A^{3}}{3} - \mathbf{L}, \exists \exists \forall \overline{Y_{P}Z_{S}} \langle \langle 1 \rangle$$

$$\therefore r = \sqrt{Y_{P}Z_{S}} = l\sqrt{(R + jwl)(G + jwc)}$$

即信号在传输线中的传输速度

$$v = \frac{w}{b} = \frac{1}{\sqrt{LC}}$$

单元线长的传输延迟

$$t_{pd} = \frac{1}{v} = \sqrt{LC}$$

可见,传输线上串联电感越大,并联电容越大,信号的传输速度越低,即传延迟时间越长。

# 3.3. 传输线的分类

传输线可分为非平衡式传输线和平衡式传输线,而非平衡式应用最多。

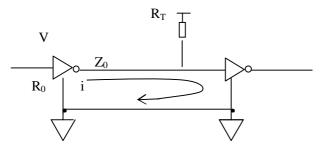

# 3.3.1. 非平衡式传输线

下图为典型的非平衡式传输线电路。

信号跃变时,电流回路中的电流也是变化的,它将产生地线回路的电压降,构成地线回路噪声。它也成为系统中其他非平衡式传输线接收器的噪声源,从而降低系统噪声容限。

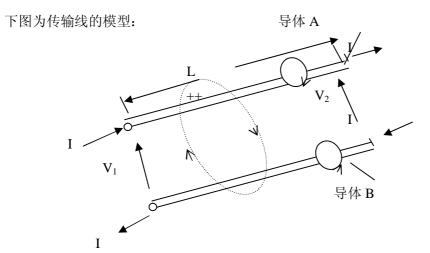

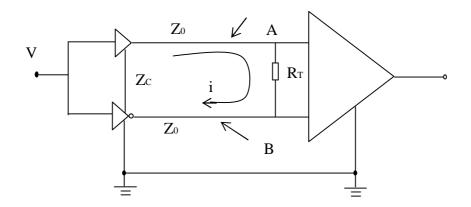

### 3.3.2. 平衡式传输线

下图为典型的平衡式传输线电路。

$Z_0$ 为 A、B 线对地的特性阻抗, $Z_C$ 为 A 线与 B 线之间的特性阻抗。

$Z_{C}=2Z_{0}$ (1-0.374 $e^{-.29s/h}$ )——带状差分; $Z_{C}=2Z_{0}$ (1-0.48 $e^{-0.96s/h}$ )——微带差分。

对于微带线,h指微带线到参考层距离;对于带状线,h指两参考层之间距离。

S 在两种情况下,均指两差分线之间的距离。

线 A、B 上传输的信号电压、电流值相等,但相位相反。

要点是 Zc均匀。

与非平衡式相比, 只产生极小的地线回路噪声。

如上图, 平衡式传输线不会对其他线路产生噪声, 同时也不易受系统其他线路产生的噪声

的干扰。

A和B的差分信号也不会在C线上产生噪声。

## 3.4. 常用传输线

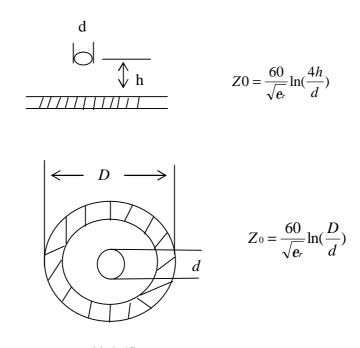

#### 3.4.1. 圆导线

同轴电缆

注: 圆导线的第一种情况,h 指导线到参考层的距离,d 是导线的外径,  $\varepsilon$  <sub>г</sub> 是介质的介电常数;第二种情况同轴电缆,D 指外导体的外径,d 指内导体的内径,  $\varepsilon$  <sub>г</sub> 是介质的介电常数;第三种情况带状电缆,D 指信号线与地线两中心点的间距,d 指信号缆内导线的外径。

#### 3.4.2. 微带线

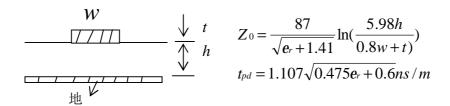

#### 3.4.2.1. 一般微带线

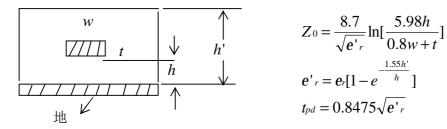

#### 3.4.2.2. 埋入式微带线

$$Z_0 = \frac{8.7}{\sqrt{e'_r}} \ln\left[\frac{5.98h}{0.8w + t}\right]$$

$$e'_r = e_r \left[1 - e^{-\frac{1.55h'}{h}}\right]$$

$$t_{pd} = 0.8475\sqrt{e'_r}$$

#### 3.4.3. 带状线

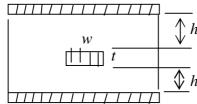

#### 3.4.3.1. 对称式带状线

注:中间信号到带,上下层为参考层。

# $z_0 = \frac{60}{\sqrt{e_r}} \ln\left[\frac{1.9(2h+t)}{0.8w+t}\right]$ $t_{pd} = 1.017\sqrt{e_r}$

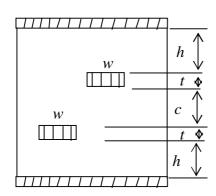

#### 3.4.3.2. 非对称式带状线

$$Z_0 \frac{80}{\sqrt{e_r}} \ln \left[ \frac{1.9(2h+t)}{0.8w+t} \right] * \left[ 1 - \frac{h}{4(h+t+c)} \right]$$

$$t_{pd} = 1.017 \sqrt{e_r}$$

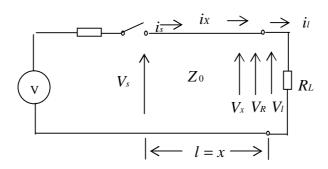

# 3.5. 反射和匹配

## 3.5.1. 反射系数

信号传输到终端时,其能量应保持不变,即到达终端的能量等于负载吸收的能量+没有被 负载吸收的能量

到达终端的能量  $P_X=i_X \cdot V_X={V_X}^2/Z_0$

负载吸收的能量  $P_L=i_L \cdot V_L=V_L^2/R_L$

没有被负载吸收的能量(反射能量)  $P_R = i_R \cdot V_R = V_R^2 / E_0$

$i_L = i_x - i_r$

$V_L = i_L * R_L = V_X + V_R$

$$\mathbf{Q} \mathbf{i}_{X} = \frac{V_{X}}{Z_{0}}$$

$$\mathbf{i}_{R} = \frac{V_{R}}{Z_{0}}$$

$$\therefore \mathbf{i}_{L} = \frac{V_{X}}{Z_{0}} - \frac{V_{R}}{Z_{0}} = \frac{V_{X} - V_{R}}{Z_{0}}$$

$$\frac{V_{X} + V_{R}}{R_{L}} = \frac{V_{X} - V_{R}}{Z_{0}}$$

$$V_{X} \cdot \left(\frac{1}{Z_{0}} - \frac{1}{R_{L}}\right) = V_{R}\left(\frac{1}{Z_{0}} + \frac{1}{R_{L}}\right)$$

$$\therefore V_{R} = V_{X} \cdot \frac{\frac{R_{L} - Z_{0}}{R_{L} + Z_{0}}}{\frac{R_{L} + Z_{0}}{R_{L} + Z_{0}}} = V_{X} \cdot \frac{R_{L} - Z_{0}}{R_{L} + Z_{0}}$$

$$\therefore \mathbf{r}_{VL} = \frac{V_{R}}{V_{X}} = \frac{R_{L} - Z_{0}}{R_{L} + Z_{0}} = \mathbf{r}_{L}$$

同样可得

$$r_S = \frac{R_S - Z_0}{R_S + Z_0}$$

其中 $\rho_S$  是源端的反射系数, $\rho_L$  是负载端的反射系数。

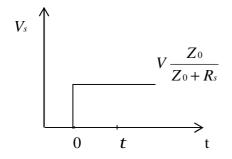

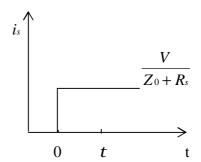

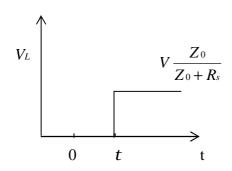

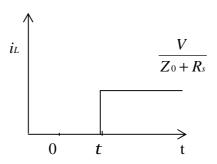

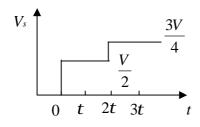

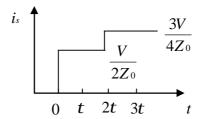

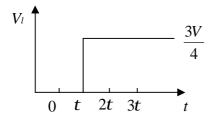

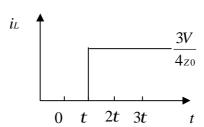

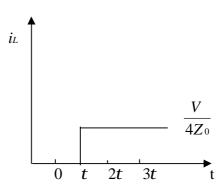

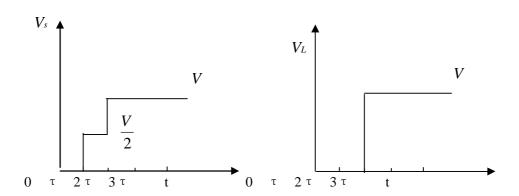

#### 3.5.2. 反射的计算:

当  $R_L > Z_0$ ,假定  $R_L = 3Z_0$ ,且  $R_s = Z_0$ ,则

$$V_{S} = V \frac{Z_{0}}{Z_{0} + R_{S}} = \frac{V}{2}$$

$$\overline{m} r_{L} = +\frac{1}{2}, \quad r_{S} = 0$$

$$V_{R} = r_{L} \bullet V_{X} = \frac{1}{2} \bullet \frac{V}{2} = \frac{V}{4} \quad (t = t)$$

$$V_{L} = V_{X} + V_{R} = \frac{V}{2} + \frac{V}{4} = \frac{3V}{4} \quad (t = t)$$

进而  $V_{S} = V_{S} + V_{R} + r_{S} V_{R} = \frac{V}{2} + \frac{V}{4} = \frac{3V}{4} \quad (t = 2t)$

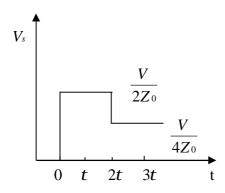

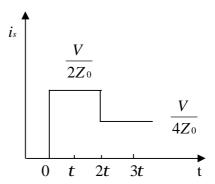

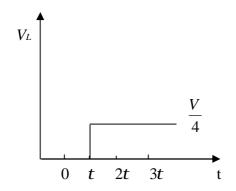

当  $R_L < Z_0$  假定  $R_L = Z0/3$ ,且  $R_S = Z_0$ ,则

$$V_{S} = V \cdot \frac{Z_{0}}{Z_{0} + R_{S}} = \frac{V}{2}$$

而  $r_{L} = -\frac{1}{2}$   $r_{S} = 0$

$V_{R} = -\frac{V}{4}(t = t)$

$V_{L} = V_{X} + V_{R} = \frac{V}{2} - \frac{V}{4} = \frac{V}{4}(t = t)$

进而  $V_{S} = V_{S} + V_{R} + r_{S}V_{R} = \frac{V}{2} - \frac{V}{4} = \frac{V}{4}(t = 2t)$

实际中, $R_S$  〉 $Z_0$ ,始端反射同样可计算。如果要消除始端反射,那么在线的始端串一电阻  $R_S$ ',使  $R_{S^+}$   $R_S$ ' =  $Z_0$ ,则  $\rho$  s=0 ,  $\rho$  L=1

ρ s、ρ μ 取不同值,线上各点波形都可计算出来。

#### 3.5.3. 传输线的临界长度

信号从始端传输到终端,反射再返回到始端即2tpd时间等于信号上升边时间。

$$t_r=2 t_{pd}$$

所以  $t_{pd}=t_r/2$

此情况下的线长定义为传输线的临界长度。

设临界线长为1则:

$$l \cdot v = t_{pd} = t_r/2$$

v——传输速度(6nS/m)

$l=t_r/2v$

当  $t_r=3$ nS 则: L=3nS/(2\*6nS/m)=1/4m=25cm

实际的物理意义是:线长大于 25cm 时为长线,也就是反射在平顶上;线长小于 25cm 时,可视为短线,反射在跃变位置上,对波形影响不大。

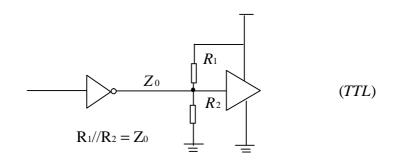

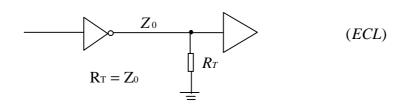

#### 3.5.4. 终端的匹配和端接

#### 3.5.4.1. 终端电阻并联匹配

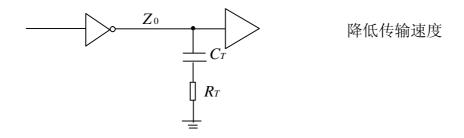

#### 3.5.4.2. 终端阻容式并联匹配

$R_T+X_{CT}=Z$   $C_T$ 选择:  $T_{RC}>3t_{pd}$

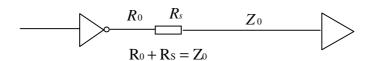

#### 3.5.4.3. 始端串联匹配

功耗低,但只有终端波形正常,始端和中间只有 V/2,不可带负载

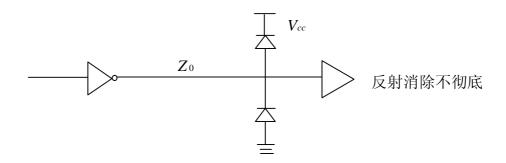

#### 3.5.4.4. 二极管钳位

注: 3.5.4.2 节、3.5.4.3 节、3.5.4.4 节还可参见信号完整性小组的《TTL/CMOS 通用设计规范》

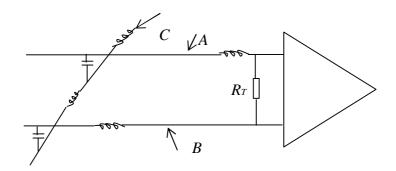

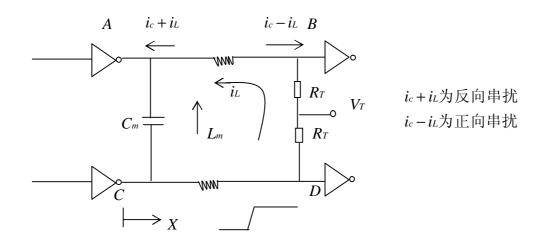

## 3.6. 串扰: 串扰模型图如下

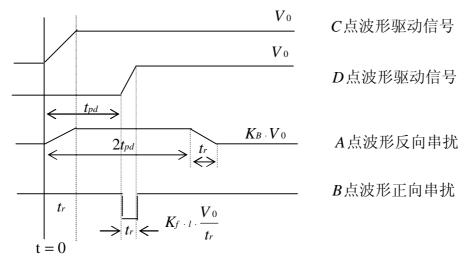

设CD上有信号,AB静止。各点波形

$$K_f = -\frac{1}{2} (\frac{L_m}{Z_0} - C_m Z_0)$$

$$K_b = \frac{1}{4t_{vd}} (\frac{L_m}{Z_0} + C_m Z_0)$$

L<sub>m</sub>——单位线长的互感

Cm——单位线长间电容

Z<sub>0</sub>——特性阻抗

*l*──线长

t<sub>nd</sub>——线的传输延迟

平行线和重叠带,串抗都一样,只是  $L_m$ 、 $C_m$ 不同,平行线  $L_m$ 大些,重叠线  $C_m$ 大些。 从表达式可知正向串抗的宽度为  $t_r$ 。幅度与 L、 $V_0$ 成正比,与  $t_r$ 成反比。反向串抗的宽度为  $2(t_{r}+t_{pd})$ ,幅度与  $V_0$ 成正比, $L_m$ 、 $C_m$ 越大,幅度也越大。

## 3.7. 负载效应

#### 3.7.1. 直流负载和交流负载

直流负载指驱动器推传输线后,端接电阻及接受门所需的直流电流值,这个值必需考虑是 否超过驱动器的直流负载能力。

交流负载指驱动器所推的线及接受门的电容值,电容增大, $t_r$ 、 $t_{pd}$  也增大,系统中主要受限于交流负载。

#### 3.7.2. 最小间隔

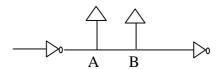

A、B 两点的最小间隔是为了 A、B 两点的容性反射波即将互相影响,而又不互相影响时的线长( $L_{MIN}$ ),目的是不使反射波叠加。

L<sub>MIN</sub>=0.85tr/tpd 可见负载应尽量分散

#### 3.7.3. 集中负载

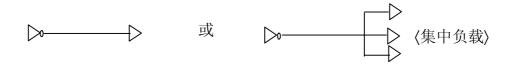

传输线上负载相对集中,单负载或负载组之间的距离 $>L_{MIN}$ ,反射互不影响, $Z_0$ 也不变化,分支线长度小于传输线临界长度,集中负载应尽量放置靠近终端。

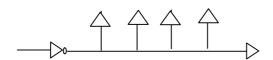

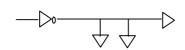

#### 3.7.4. 分布负载

负载间隔<L $_{MIN}$ ,反射波叠加,使 tpd 增大, $Z_0$ 减小,引起失配

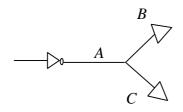

## 3.7.5. 径向负载

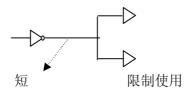

分支线长>传输线临界长度  $Z_0'=Z_0/N$  N——分支数 系统设计中应严格限制使用

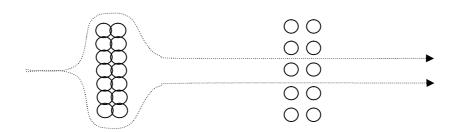

## 3.8. 负载驱动方式

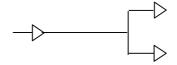

#### 3.8.1. 点对点

如上图中的方法是最好的方法,高速信号或时钟信号应采此方法

#### 3.8.2. 串推

分支线长较短

#### 3.8.3. 星型

严格限制使用 (三分支均长)

## 3.8.4. 扇型

# 3.9. 传输线损耗和信号质量

#### 3.9.1. 集肤效应

直流电流流过导体时,截面积上的电流密度是均匀的,但高频交变电流流过导体时,电流密度越靠近表面越大,设集肤效应的表面深度为 D。

$$D = K \frac{1}{\sqrt{f}}$$

$$K = \frac{1}{\sqrt{pms}}$$

因为集肤效应减小了导体传输电流的有效截面积,所以提高频率,将增加导线等效电阻,而增加信号损耗。

#### 3.9.2. 邻近效应

两个邻近导体中的电流的相互吸引(或排斥)将导致电流密度的重新分布,使电流传输的

有效截面积减小,增加了导线电阻而增加信号损耗,邻近效应与导体的几何形状、导体间 距和频率有关。

#### 3.9.3. 辐射损耗

频率提高后,前面两种电阻的增大可看成是热的辐射损耗,此外,还存在电磁辐射、交变 电场和交变磁场,向外辐射能量而使信号损耗。同轴电缆中的幅射损耗小,是因为芯电流 磁场与屏蔽层电流磁场相互抵销了,辐射损耗与外部介质的  $\mu$  、  $\epsilon_r$  密切相关。

#### 3.9.4. 介质损耗

介质中流过高频漏电流,将使信号受到损耗,tr将增大,tpd增大,一般分析传输线时,都是建立在无损耗条件下的,当频率变到一定值时,有损耗传输问题应认真考虑。

# 第4章 直流电源分布系统设计

## 4.1. 基本概念

#### 4.1.1. 电源分布系统

Power Distribution System (PDS)

#### 4.1.2. 平面

当电源、地层之间存在足够的去耦电容后,其交流阻抗极小,交流信号可以在任何一层上传输。换言之,对于交流信号而言,电源、地层是没有区别的,可以统称为平面(Plane)。

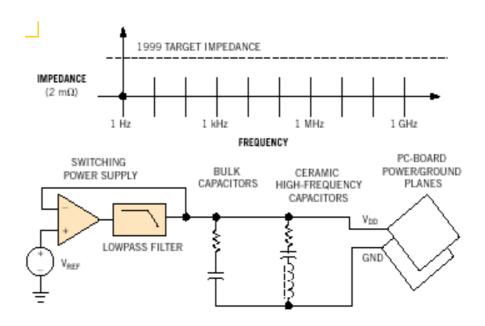

# 4.1.3. 平面(Plane)为电流回路提供最低阻抗回路 PDS 阻抗

$$Z_{PDS} = \frac{$$

电源电压×允许电压波动的比率(百分数)÷100 需要的电流

## 4.2. 设计目标

- 4.2.1. 为数字信号提供稳定的电压参考;

- 4.2.2. 为逻辑电路提供低阻抗的接地连接;

- 4.2.3. 为逻辑电路提供低阻抗的电源连接;

- 4.2.4. 为电源和地提供低交流阻抗的通路;

#### 4.2.5. 为数字逻辑电路工作提供电源

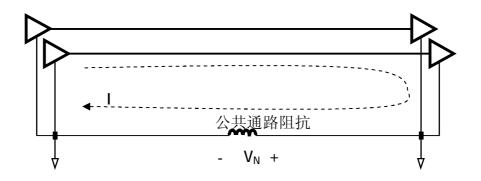

#### 4.2.5.1. 公共通路阻抗将产生电源和地电位差

$X_{PSW} = ESR + 2\pi f \times ESL$

**ESR**——电源分布系统寄生电阻。低频或直流情况下,是造成电源电位差的主要原因。

ESL——电源分布系统寄生电感。高频情况下,交变电流将在寄生电感上产生电源电位差,其幅度远大于寄生电阻的影响。

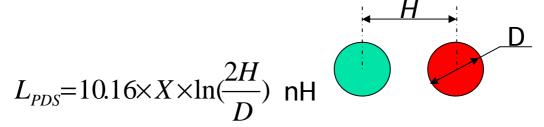

#### 电源分布系统寄生电感

a) 两条平行的电源和地圆导线

X — 电源分布线长度, in

H — 电源分布线平均间距, in

D — 电源分布线直径, in

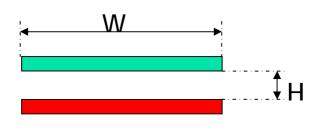

b) 多层平行堆叠的扁平带状的电源和地线

$$L_{PDS} = 31.9 \times \frac{X \times H}{W(N-1)}$$

**nH**

N=2

X 一 电源分布线长度, in

H 一 电源分布线平均间距, in

W - 电源分布线宽度, in

N - 电源和地层数

#### 4.3. 一般设计规则

- Ø PDS 必须为电路正常工作提供稳定的、无噪声的电压和电流。

- Ø 为数字信号提供稳定的电压参考。

- Ø 对于每一个电路来说,PDS 应当被视为独立的、相互隔离的,以保证噪声不能通过 PDS 耦合到其他线路。

- **Ø** 电源、地平面(线)之间应具有尽可能小的交流阻抗。

- Ø PDS 必须为信号提供无干扰的回流通路。

- **Ø** 电源、地平面应同时具备空间电场的屏蔽作用。

- Ø 尽可能采用平面设计,或保持电源和地线尽可能短和宽,避免"梳状"地线。

- ② "背靠背"的电源和地层设计,具有最小的 PDS 阻抗,并具备高频去耦作用,能有效抑制高频噪声。

- Ø 配置足够的、均匀分布的去耦电容。

- Ø 在数模混合设计中,应为数字电路和模拟电路分别提供独立的 PDS。

- ▼ 大量的不同逻辑电平、不同噪声容限的电路(如 TTL、ECL 等)在混合设计中,应为它们分别提供独立的 PDS。

- Ø 不同的电源、地层应相对隔离,不直接叠压。

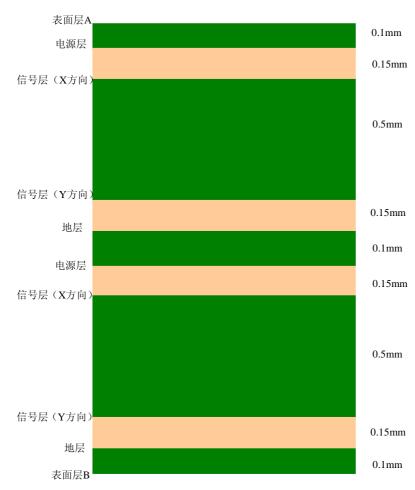

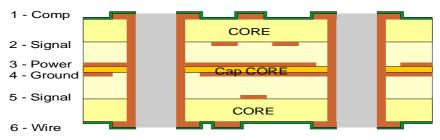

#### 4.4. 多层板的叠层结构

#### 4.4.1. 叠层结构的设计主要考虑以下因素

Ø 稳定、低噪声、低交流阻抗的 PDS

- Ø 传输线结构要求

- Ø 传输线特性阻抗要求

- Ø 串扰噪声抑制

- Ø 空间电磁干扰的吸收和屏蔽

- Ø 结构对称,防止变形

## 4.4.2. 在高速数字设计中的一般规则是

电源层数 + 地层数 = 信号层数 电源层和地层尽可能成对设计,并至少有一对是"背靠背"设计 采用带状线结构,关键信号传输应采用对称带状线。

#### 多层板的叠层实例

ł

古古出

# 4.5. 电流回路

## 4.5.1. 基本概念

所有电流必须有流回源的回路。该回路的产生会自动寻找最小阻抗的路径。通常在具有电源/地层平面的 PCB 结构中,会直接在信号线下方的平面上(电源或地)。该回流信号(电流)与原信号(电流)幅度相同、方向相反。

$$i(D) = \frac{I_0}{p \times H} \times \frac{1}{1 + (D/H)^2}$$

$I_0$  — 信号总电流,A

H — 信号线到参考平面的距离, m

D — 观测点到信号线中心的垂直距离, m

i(D)—观测点的回流电流密度, A/in

#### 4.5.2. 环路面积

信号和回流信号通路构成了一个闭合回路。随着环路面积的增大,将产生更多的差模辐射噪声,且更易于受外界干扰的影响。

$$E = \frac{2.6 \times (A \times I_L \times f^2)}{R} \qquad \mu V/m$$

A — 环路面积, cm<sup>2</sup>

I<sub>L</sub> — 环路电流, A

f — 频率,MHz

R — 观测点到电场中心的距离, m

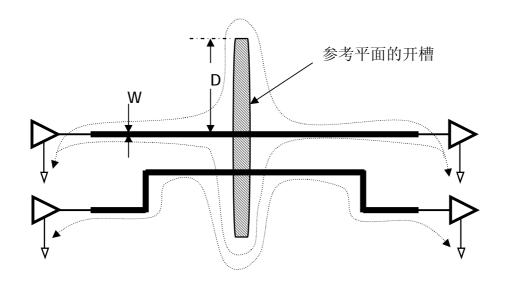

#### 4.5.3. 参考平面的开槽

不适当的参考平面的开槽,将增加信号的环路面积。

#### 4.5.4. 连接器的隔离盘

连接器在参考平面上不适当的隔离盘,将增加信号的环路面积。

信号环路面积增加,将产生额外的感抗,减慢信号边沿速率,并在临近信号线上产生互感串扰。

如上 4.5.3 图所示:

$$L = 5 D \ln(\frac{D}{W}) 53 \cap H$$

zte  $\pm \%$

$$T_{10-90L/R} = 2.2 \times \frac{L}{2 \times Z_0}$$

$$Tr = \sqrt{(T_{10-90L/R})^2 + (T_{10-90})^2}$$

(长线)

$$T_r = 3.4 \times \sqrt{L \times C} \qquad (53)$$

$$V_{crosstalk} = \frac{\Delta V \times L}{T_r \times Z_0} \qquad (\text{K$\sharp$})$$

(短线)

$$V_{crosstalk} = \frac{1.52 \times \Delta V \times C \times L}{(T_{\pi})^2}$$

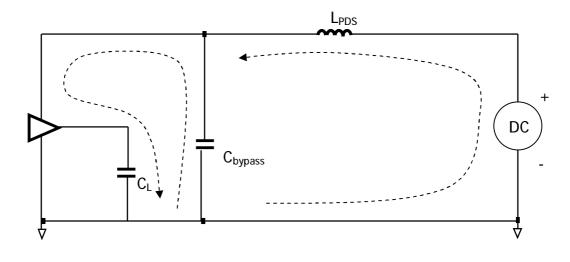

## 4.6. 去耦电容极其应用

#### 4.6.1. 去耦电容

#### 4.6.1.1. 去耦作用

消除高频开关电路产生的 RF 能量,为电路提供一个低阻抗本地直流源,而完成去耦作用的前提,是保证在电源分布系统具有较低的交流阻抗。

- 4.6.2. 低频大容量去耦电容(BULK)

- 4.6.2.1. 在所有的信号管脚开关同时处于最大的容性负载条件时,提供稳定的直流电压、电流。

- 4.6.2.2. 通常选用大容量钽电容,电压额定值一般为电路额定工作电压的5倍

- 4.6.2.3. 放置位置

- a) 时钟电路附近

- b) 输入/输出连接处

- c) 大功耗电路附近

- d) 远离电源馈入点的位置

#### 4.6.2.4. 低频大容量电容的选择步骤

- a) 计算电路的最大交变电流(p/)

- b)给出电路所允许的最大电源电位差噪声( pV)

- c) 计算电路所允许的最大  $X_{MAX} = |xV/|xI|$

- d)给出电源、地分布线的寄生电感 L<sub>PSW</sub>

- f) 计算电源、地分布线的最高响应频率 F<sub>PSW</sub>

$$F_{PSW} = \frac{X_{MAX}}{2 \times \pi \times L_{PSW}}$$

g) 计算去耦所需要的最小电容值 Cbypass

$$C_{bypass} = \frac{1}{2 \times p \times F_{PSW} \times X_{MAX}}$$

h) 根据去耦电容的引脚电感 Lc, 计算其最高响应频率 Fbypass

$$F_{bypass} = \frac{X_{MAX}}{2 \times p \times L_{C}}$$

#### 4.6.2.5. 低频大容量电容的选择实例

某 5V CMOS 电路板有 100 个门,分别驱动 10pF 负载,边沿时间为 5ns。电源分布线的电感为 100nH。

$$\Delta I = NC \frac{\Delta V}{\Delta t} = 100 \times 10 \, pF \times \frac{5V}{5ns} = 1A$$

$$\Delta V = 0.100V$$

$$X_{MAX} = \frac{\Delta V}{\Delta I} = 0.1\Omega$$

$$L_{PSW} = 100nH$$

$$F_{PSW} = \frac{X_{MAX}}{2pL_{PSW}} = 159 \, KHz$$

$$C_{bypass} = \frac{1}{2pF_{PSW} X_{MAX}} = 10 \, mF$$

设电容引脚电感 L<sub>C</sub>=5nH,则

$$F_{bypass} = \frac{X_{MAX}}{2pL_C} = 3.18 MHz$$

## 4.6.3. 高频去耦电容

#### 4.6.3.1. 高频去耦电容为电路提供本地的低阻抗直流源

#### 4.6.3.2. 高频去耦电容的阻抗必须小于 X<sub>PSW</sub>

选择高频去耦电容的一般原则

a) 自谐振频率>需抑制的时钟谐波频率

提供电路瞬态工作能量

高频去耦电容的选择步骤

计算系统在高频下正常工作所能允许的电感 Ltot

$$L_{tot} = \frac{X_{MAX}}{2 \times p \times F_{knee}} = \frac{X_{MAX} T_r}{p}$$

- b) 给出电容的引脚电感 LC

- c) 计算并联电容的数目 N

$$N = \frac{L_{C}}{L_{tot}}$$

d) 计算并联电容值 C<sub>Parallel</sub>

$$C_{parallel} = \frac{1}{2 \times p \times F_{bypass} \times X_{MAX}}$$

e) 计算每一个电容的值 Celement

$$C_{element} = \frac{C_{parallel}}{N}$$

高频去耦电容的选择实例

某 5V CMOS 电路板有 100 个门,分别驱动 10pF 负载,边沿时间为 5ns。电源分布线的电感为 100nH。设电容引脚电感  $L_C=5nH$ 。

$$T_r = 5ns$$

$X_{MAX} = 0.1\Omega$   $F_{bypass} = 3.18MHz$

$$L_{tot} = \frac{X_{MAX} \times T_r}{p} = 0.159nH$$

$$N = \frac{L_C}{L_{tot}} = 32$$

$$C_{parallel} = \frac{1}{2 \times p \times F_{bypass} \times X_{MAX}} = 0.5 \, \text{mF}$$

$$C_{element} = \frac{C_{parallel}}{N} = 0.016 \text{mF}$$

#### 4.6.4. 多层片式陶瓷电容的材料选择

#### 4.6.4.1. 通常使用的材料有三种

- a) NP0

- b) X7R

- c) Z5U

其中, X7R 是去耦应用的最佳选择,介电常数介于 NPO 和 Z5U 之间;相对于 Z5U, 具有较好的温度和电压系数;相对于 NPO,具有较高的 ESR 和较差的温度和电压系数; 相同的封装下,电容值的范围比 NPO 宽。

#### 4.6.5. 表面贴装电容的布局和布线

#### 4.6.5.1. 不同的布局,产生的寄生电感的数值相差很大

应采用较大的过孔

电容焊盘到过孔的引线应尽可能短和宽

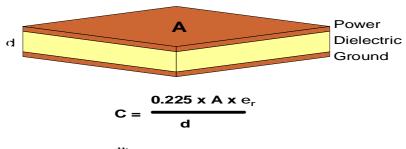

#### 4.6.6. 多层印制板中的平面电容

4. 6. 6. 1. 多层 PCB 中直接相邻("背靠背")的电源和地平面构成了一个具有最小交流阻抗的平面电容。

$$C_{plane} = \frac{0.225 \times e_r \times A}{d} \quad PF$$

A — 平面重叠面积, in<sup>2</sup>

d — 间隔距离, in

ε<sub>r</sub> — 绝缘介质的介电常数

例如: 当采用 FR-4 材料 (ε = 4.5),

d=0.01 in 时,

$C_{plane} = 100 pF/in^2$

注: 这里的  $100 pF/in^2$  是指以一个平方英寸双层平面具有的电容, $C_{plane}$  的单位是 PF 或 F 等。

平面电容具有最好的高频特性

#### 4.6.7. 埋入式电容

#### 4.6.7.1. 埋入式电容原理

若 $e_r = 90$ ,则C = 5nf/in<sup>2</sup>

#### 4.6.7.2. 埋入式电容设计

高速数字设计中典型的 PDS

6 Layer / 3 Core Construction

## 4.7. 噪声抑制

- 4.7.1. 系统电源变化

- 4.7.2. 系统电源的电位差

- 4.7.3. 系统逻辑地的电位差

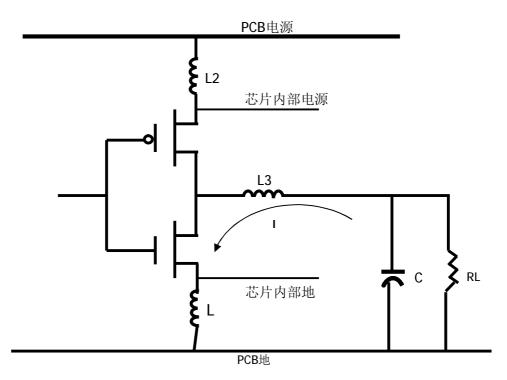

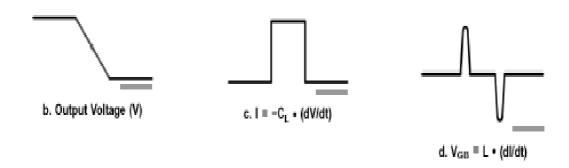

#### 4.7.4. 地电平抖动

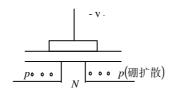

地电平抖动(GROUND BOUNCE——GB)的起因

#### GROUND BOUNCE 现象

抑制 GROUND BOUNCE 的一般方法:

- Ø 采用较小的封装形式;

- Ø 采用适当的电源、地针数目和合理布局;

- Ø 减小输出电压摆幅;

- Ø 限制同时同相转换状态的输出单元数目;

- Ø 增加传输线的特性阻抗;减少容性负载;

- **Ø** 在输出端串接阻尼电阻。

#### 附录:

#### 参考文献

- 1) Skilling, H.H., Electric Transmission Lines, New York . McGraw-Hill, 1951

- 2) Kaupp.H.R. *Characteristics of Microstrip Transmission Lines*, IEEE Transactions on Electronic Computers. Vol. Ec-16 NO2 April 1967, pp.185-193

- 3) Cohn, S.B. *Characteristics Impedance of the Shielded Strip Transmission Line*, Transactions IRE. Vol.. MTT-2, July 1954. pp52-57

- 4) DeFalco, J.A., *Reflections and Crosstalk in Logic Circuit Interconnections*, IEEE Spectrum, July 1970.pp44-50

- 5) Blood, Jr., William R. MECL System Design Handbook, 4th Edition, Motorola Inc., 1988.

- B.L.Hart, Digital Signal Transmission Line Circuit Technology, Van Nostrand Reinhold, New York, 1988.

- 7) Charles S. Walker, *Capacitance, Inductance and Crosstalk Analysis*, Artech House, Norwood, Mass., 1990

- 8) T.C.Edwards, Foundations for Microstrip Circuit Design, John Wiley, New York, 1981.

- 9) Harlan Howe, Stripline Circuit Design, Artech House, Norwood, Mass., 1974

- 10) S.R.SESHARI, Fundamentals of Transmission Lines and Electromagnetic Fields *Addison-Wesley, Reading, Mass.*, 1971

- 11) Clyde F.Coombs, Jr., Ed., Printed Circuits Handbook, McGraw Hill, New York, 1988.

- 12) Bernard S. Matisoff, Handbook of Electronics Packaging Design and Engineering, 2nd edition, Van Nostrand Reinhold, New York, 1990

- Raymond H. Clark, Printed Circuit Engineering: Optimizing for Manufacturabillity, Van Nostrand Reinhold, New York, 1989.

- 14) Henry W. Ott, Noise Reduction Techniques in Electronic Systems, John Wiley, New York, 1988.

- 15) Bernhard Keiser, Principles of Electromagnetic Compatibility, 3rd edition, Artech House, Norwood, Mass., 1987.

- 16) Clayton R. Paul, Introduction to Electromagnetic Compatibility, John Wiley, New York, 1992.

- 17) Frederick E. Terman, Radio Engineers Handbook, McGraw-Hill, New York, 1943

- 18) Robert A. Pease, Troubleshooting Analog Circuit, Butterworth-Neinemann, Stoneham, Mass., 1991.

- 19) DeHon.A. And Knight.T., Automatic Impedance Control, 1993 IEEE International Solid State Circuits Conference Digest of Technical Papers, IEEE, New York, 1993.

- 20) Dworsky, L., Modern Transmission Line Theory and Applications, Robert E. Krieger Publishing Company, Malabar, Florida, 1988.

- 21) Gabara, T., and Thompson, D., Ground Bounce Control in CMOS Integrated Circuitry, 1988, IEEE International Solid State Circuits Conference Digest of Technical Papers, IEEE, New York, 1988.

- 22) 《PCI Local Bus Specification——Production Version》, Revision 2.1

- 23) 《CX27470 Traffic Stream Processor—Reference Manual》, Version 1.0

- 24) 《MECL System Design Handbook》, Fourth Edition, William R. Blood, Jr.

- 25) 《LVDS Owner's Manual》, 2nd Edition

- 26) 《Noise Reduction Techniques in Electronic Systems》 Henry W. Ott, John Wiley, New

- York, 1988.

- 27) 《Principles of Electromagnetic Compatibility》, Bernhard Keiser, 3rd edition, Artech House, Norwood, Mass., 1987.

- 28) 《Automatic Impedance Control》, DeHon.A., And Knight.T., 1993 IEEE International Solid State Circuits Conference Digest of Technical Papers, IEEE, New York, 1993.

- 29) 《Ground Bounce Control in CMOS Integrated Circuitry》, Gabara, T., And Thompson, D., 1988, IEEE International Solid State Circuits Conference Digest of Technical Papers, IEEE, New York, 1988.